Реферат: ПЛИС Xilinx семейства Virtex™

Реферат: ПЛИС Xilinx семейства Virtex™

4.3.5. Буферы с тремя состояниями

Каждый КЛБ Virtex содержит два буфера с тремя состояниями, которые нагружены на внутренние шины (см. также п. 4.4.4 «Специальные трассировочные ресурсы»). Каждый буфер BUFT имеет независимый вход управления с третьим состоянием и независимый входной контакт.

4.3.6. Блочная память (Block RAM)

В FPGA Virtex встроена особая блочная память (Block Select RAM) большой емкости. Она создана в дополнение к распределенной памяти небольшой емкости (Select RAM), реализованной на таблицах преобразования (Look Up Table RAM — LUTRAM).

Блоки памяти Block Select RAM+ организованы в виде столбцов. Все устройства Virtex содержат два таких столбца, по одному вдоль каждой вертикальной стороны кристалла. Эти колонки увеличивают полный размер кристалла. Каждый блок памяти равен по высоте четырем КЛБ, таким образом, микросхема Virtex, имеющая 64 КЛБ по высоте, содержит 1-6 блоков памяти на колонку и 32 блока памяти в целом. В Табл. 5 приводятся емкости блочной памяти для различных кристаллов Virtex.

Таблица 5. Емкость блочной памяти.

| Кристалл Virtex |

Число блоков |

Общий объем блочной памяти [бит] |

XCV50 |

8 | 32 768 |

| XCV100 | 10 | 40 960 |

| XCV150 | 12 | 49 152 |

| XCV200 | 14 | 57 344 |

| XCV300 | 16 | 65 536 |

| XCV400 | 20 | 81 920 |

| XCV600 | 24 | 98 304 |

| XCV800 | 28 | 114 688 |

| XCV1000 | 32 | 131 072 |

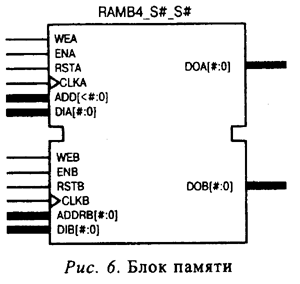

Каждый блок памяти, как показано на Рис. 6, это полностью синхронное двухпортовое ОЗУ с независимым управлением для каждого порта. Размерность шины данных для обоих портов может быть сконфигурирована независимо, что позволяет создавать преобразователи размерности шины. В Табл. 6 показаны возможные соотношения размерностей шин данных и адреса.

В кристаллах Virtex созданы специальные трассировочные ресурсы для связи блочной памяти с блоками КЛБ и другими блоками памяти.

Таблица 6. Соотношение шин адреса и данных

Разрядность |

Глубина | Шина адреса | Шина данных |

| 1 | 4096 | ADDR<11:0> | DATA<0> |

| 2 | 2048 | ADDR<10:0> | DATA<1:0> |

| 4 | 1024 | ADDR<9:0> | DATA<3:0> |

| 8 | 512 | ADDR<8:0> | DATA<7:0> |

| 16 | 256 | ADDR<7:0> | DATA<15:0> |

4.4. Программируемая трассировочная матрица

Быстродействие проекта, рассчитанного для наихудшего случая, ограничивает величина задержки для наиболее длинной трассы. Поэтому архитектура трассировочных ресурсов и программы размещения и трассировки создавались с учетом использования их в едином процессе оптимизации. Этот совместный процесс оптимизации минимизирует наиболее длинные пути и, таким образом, создает проект с наилучшей системной производительностью.

Кроме того, совместная оптимизация сокращает время компиляции, так как программное обеспечение и архитектура микросхемы создавались с учетом наилучшего взаимодействия. Циклы проектирования, таким образом, сократились благодаря более коротким временам каждой из итераций всего процесса.

4.4.1. Локальные связи

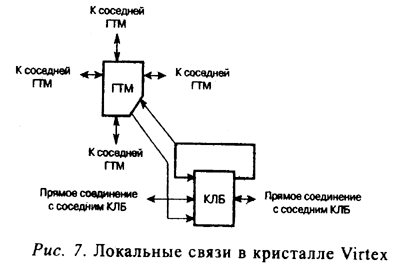

Как показано на Рис. 7, в кристалле Virtex созданы локальные трассировочные ресурсы, называемые VersaBlock. Они позволяют реализовать три типа соединений:

1. Связи между таблицами преобразования (LUT), триггерами и главной трассировочной матрицей (ГТМ).

2. Внутренние обратные связи КЛБ, которые создают высокоскоростные связи с таблицами преобразования в рамках одного КЛБ и позволяют соединять их в виде цепочек с минимальными задержками распространения сигналов.

3. Прямые трассы, которые создают высокоскоростные соединения с соседними по горизонтали КЛБ, избегая при этом больших задержек, присущих трассам ГТМ.

4.4.2. Трассировочные ресурсы общего назначения

Большинство связей в кристаллах Virtex реализуются с помощью трассировочных ресурсов общего назначения, и, следовательно, большая часть ресурсов межсоединений связана с этим типом трассировочной иерархии. Трассировочные ресурсы общего назначения расположены в виде горизонтальных и вертикальных трассировочных каналов и размещены в непосредственной близости от строк и столбцов матрицы, образованной блоками КЛБ. Ниже перечислены эти ресурсы:

• Примыкающая к каждому КЛБ главная трассировочная матрица (ГТМ) — это матрица переключателей, с помощью которых коммутируются горизонтальные и вертикальные трассы и посредством которых блоки КЛБ получают доступ к трассировочным ресурсам общего назначения.

• ГТМ связана в каждом из четырех направлений с соседней ГТМ посредством 24 трасс одинарной длины.

• 96 буферизованных НЕХ-линий трассируют сигналы ГТМ к шести другим ГТМ в каждом из четырех направлений. НЕХ-линии организованы в виде зигзагообразных линий. НЕХ-линии могут подключаться к источникам сигнала только в своих конечных точках или серединных (три блока от источника). Одна третья часть НЕХ-линий является двунаправленными, в то время как остальные — однонаправленные.

• 12 длинных линий являются буферизированными, двунаправленными линиями, распространяющими сигналы в микросхеме быстро и эффективно. Вертикальные длинные линии имеют протяженность, равную полной высоте кристалла, а горизонтальные длинные линии — полной ширине.

4.4.3. Трассировочные ресурсы для блоков ввода-вывода

Кристалл Virtex имеет дополнительные трассировочные ресурсы, расположенные по периферии всей микросхемы. Эти трассировочные ресурсы формируют добавочный интерфейс между КЛБ и БВВ. Эти дополнительные ресурсы, называемые VersaRing, улучшают возможности закрепления сигналов за контактами и переназначения уже сделанного закрепления, если это требование накладывается расположением сигналов на печатной плате. При этом сокращается время изготовления всего проекта, т. к. изготовление и проектирование печатной платы можно выполнять одновременно с проектированием FPGA.

4.4.4. Специальные трассировочные ресурсы

Некоторые классы сигналов требуют наличия специальных трассировочных ресурсов для получения максимального быстродействия. В устройстве Virtex специальные трассировочные ресурсы создавались для двух классов сигналов:

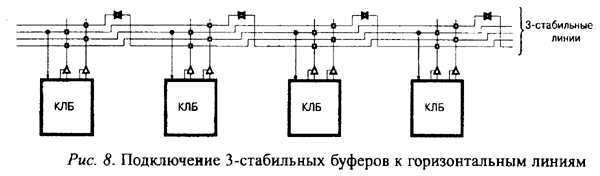

• Горизонтальные трассировочные ресурсы создавались для реализации микросхеме шин с тремя состояниями. Четыре разделенные линии шин реализованы для каждой строки КЛБ, позволяя организовывать сразу несколько шин в пределах одной строки (Рис. 8).

• Две специальные линии для распространения сигналов быстрого переноса к прилегающему КЛБ в вертикальном направлении.

4.4.5. Глобальные трассировочные ресурсы

Глобальные трассировочные ресурсы распределяют тактовые сигналы и другие сигналы с большим коэффициентом разветвления по выходу на всем пространстве кристалла. Кристалл Virtex имеет два типа глобальных трассировочных ресурсовтназываемых соответственно первичными и вторичными:

• Первичные глобальные трассировочные ресурсы представляют собой четыре специальные глобальные сети со специально выделенными входными контактами и связанными с ними глобальными буферами, спроектированными для распределения сигналов синхронизации с высоким коэффициентом разветвления и с минимальными разбегами фронтов. Каждая такая сеть может быть нагружена на входы синхронизации всех КЛБ, БВВ и Block RAM — блоков микросхемы. Источниками сигналов для этих сетей могут быть только глобальные буферы. Всего имеется четыре глобальных буфера — по одному для каждой глобальной сети.

• Вторичные глобальные трассировочные ресурсы состоят из 24 магистральных линий, 12 — вдоль верхней стороны кристалла и 12 — вдоль нижней. По этим связям может быть распространено до 12 уникальных сигналов на колонку по 12 длинным линиям данной колонки. Вторичные ресурсы являются более 'гибкими, чем первичные, т.к. эти сигналы, в отличие от первичных, могут трассироваться не только до входов синхронизации.

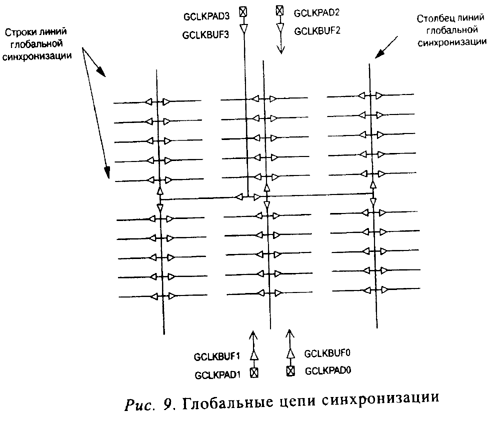

4.5. Распределение сигналов синхронизации

Как было описано выше, Virtex имеет высокоскоростные, с малыми искажениями трассировочные ресурсы для распределения сигналов синхронизации на всем пространстве микросхемы. Типичное распределение цепей синхронизации показано на Рис. 9.

В микросхему встроено четыре глобальных буфера, два — в середине верхней части микросхемы, два — в середине нижней части. Эти буферы через первичные глобальные сети могут подводить сигналы синхронизации на любой тактовый вход.

Для каждого глобального буфера имеется соответствующий, примыкающий к нему контакт микросхемы. Сигнал на вход глобального буфера может подаваться как с этих контактов, так и от сигналов, трассируемых ресурсами общего назначения.

4.5.1. Модули автоподстройки задержки (DLL)

Полностью цифровая автоподстройка задержки (DLL), связанная с каждым глобальным буфером, может устранять перекос задержек между синхросигналом на входном контакте микросхемы и сигналами на тактовых входах внутренних схем устройства. Каждая DLL может быть нагружена на две глобальные цепи синхронизации. Схема DLL отслеживает сигнал синхронизации на входном контакте микросхемы и тактовый сигнал, распределяемый внутри кристалла, затем автоматически устанавливает необходимую задержку. Дополнительная задержка вводится таким образом, что фронты сигналов синхронизации достигают внутренних триггеров в точности на один период синхронизации позже их прихода на входной контакт. Эта система с обратной связью эффективно устраняет задержку распределения сигналов синхронизации, гарантируя, что фронты синхросигналов на входе микросхемы и на внутренних тактовых входах с большой точностью синхронны.

Вдобавок, для устранения задержек, возникающих при распределении тактовых сигналов, DLL создает новые возможности управления функциями синхронизации. Модуль DLL может создавать четыре квадратурные фазы из исходного источника синхросигнала; удваивать частоту синхросигнала или делить эту частоту на 1.5, 2, 2.5, 3, 4, 5, 8 или 16.

Модуль DLL также функционирует как тактовое зеркало. Путем вывода из микросхемы сигнала с выхода DLL и последующего ввода этого сигнала снова внутрь кристалла, схема DLL может устранить разбег фаз для тактовых сигналов на уровне печатной платы, при работе с несколькими устройствами Virtex.

Чтобы гарантировать, что системная синхронизация будет нормально функционировать до момента окончания конфигурирования системы и начала штатной работы, схема DLL имеет возможность задерживать процесс конфигурирования до нормальной синхронизации с системой.

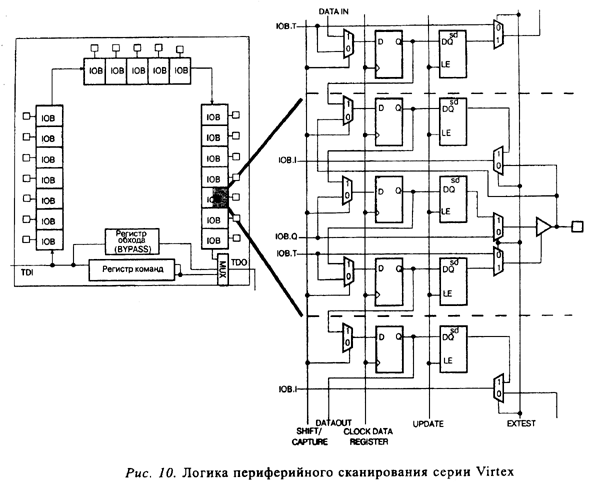

4.6. Периферийное сканирование (ПС)

Микросхемы Virtex поддерживают команды периферийного сканирования, приведенные в спецификации стандарта IEЕЕ 1149.1. Порт Test Access Port (TAP) и регистры реализованы для выполнения команд Extest, INTEST, Sample/Preload, Bypass, IDCODE, USERCODE и HIGHZ. Кроме того, порт ТАР поддерживает две внутренние сканирующие цепочки и позволяет загрузить/считать конфигурацию кристалла.

Порт ТАР использует предопределенные контакты

микросхемы и LVTTL уровни сигналов. Для того

чтобы выход TDO выдавал сигналы на уровнях LVTTL, на

контакт ![]() второго банка должно быть

подано напряжение 3.3 В. В противном случае напряжение на выходе ТDО

будет меняться в пределах от нуля до

второго банка должно быть

подано напряжение 3.3 В. В противном случае напряжение на выходе ТDО

будет меняться в пределах от нуля до ![]() .

.

Операции периферийного сканирования не зависят от конкретных конфигураций блоков ввода-вывода и типа корпуса. Все блоки ввода-вывода, включая неподключенные к контактам, рассматриваются как независимые двунаправленные контакты с тремя состояниями, в единой цепочке сканирования. Сохранение возможности осуществлять двунаправленное тестирование после конфигурирования облегчает тестирование внешних межсоединений.

В Табл. 7 приведены команды периферийного сканирования, поддерживаемые кристаллами Virtex. Внутренние сигналы могут быть проанализированы в процессе выполнения команды Extest посредством подключения их к неиспользуемым выходам блоков ввода-вывода, либо к блокам ввода-вывода, не присоединенным к контактам. Они могут быть также подсоединены к неиспользуемым выходам блоков ввода-вывода, которые определены как однонаправленные входные контакты.

Таблица 7. Инструкции периферийного сканирования

Команда |

Двоичный код | Описание |

| EXTEST | 00000 | Разрешает операцию периферийного сканирования EXTEST |

| SAMPLE/PRELOAD | 00001 | Разрешает операцию периферийного сканирования SAMPLE/PRELOAD |

| USER1 | 00010 | Доступ к определенному пользователем регистру 1 |

| USER2 | 00011 | Доступ к определенному пользователем регистру 2 |

| CFG_OUT | 00100 | Доступ к конфигурационной шине для операций считывания |

| CFG_IN | 00101 | Доступ к конфигурационной шине для операций записи |

| INTEST | 00111 | Разрешает операцию периферийного сканирования INTEST |

| USERCODE | 01000 | Разрешает считывание пользовательского кода |

| IDCODE | 01001 | Разрешает считывание ID кода |

| HIGHZ | 01010 | Переводит выходы в третье состояние во время операции BYPASS |

| JSTART | 01100 | Активизирует вход TCK порта TAP |

| BYPASS | 11111 | Разрешает BYPASS |

| RESERVED | Любой другой | Зарезервированные инструкции |

До конфигурации кристалла доступны все команды кроме USER1 и USER2. После конфигурации кристалла доступны все команды без исключения. Во время конфигурации не рекомендуется использовать команды Extest, INtest и Sample/Preload.