Реферат: ПЛИС Xilinx семейства Virtex™

Реферат: ПЛИС Xilinx семейства Virtex™

6.1.1. Подчиненный последовательный резким

В этом режиме FPGA принимает конфигурационные данные в последовательной форме от последовательного ПЗУ или от другого источника последовательных конфигурационных данных.

Данные последовательного битового потока (bitstream) должны быть установлены на входе DIN незадолго до появления нарастающего фронта сигнала, генерируемого внешним источником и подаваемого на вход CCLK.

Несколько микросхем FPGA могут быть соединены в цепочку для конфигурирования от единого внешнего источника конфигурационных данных. После того как одна из микросхем сконфигурирована, данные для следующей появляются на выходе DOUT. Изменение данных на выходе DOUT происходит после нарастающего фронта сигнала на входе CCLK.

Процесс стробирования данных, подаваемых на вход DIN по нарастающему фронту CCLK, отличается от аналогичного процесса в старых семействах микросхем FPGA, но это не приводит к возникновению проблем для смешанных конфигурационных цепочек. Такое изменение сделано для увеличения скоростей последовательного конфигурирования цепочек FPGA, состоящих только из микросхем Virtex.

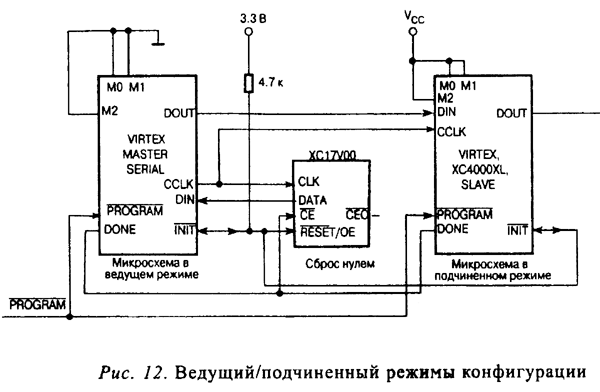

На Рис. 12 изображена полная схема, совмещающая подчиненные режимы и ведущий режим. FPGA Virtex, конфигурируемые в подчиненном режиме, должны быть подключены так же, как устройство, изображенное третьим слева.

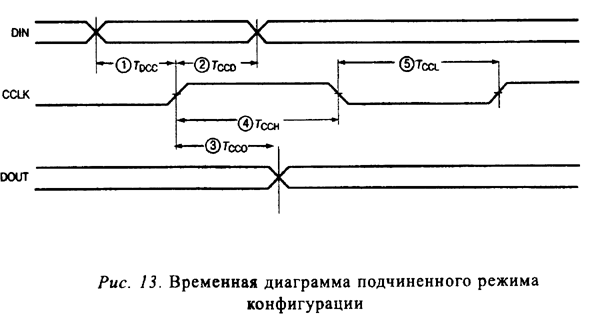

Подчиненный последовательный режим выбирается заданием кода <111> на входах режима конфигурирования (М2, Ml, М0). Внутренние высокоомные резисторы на режимных контактах «подтягивают» данные входы в состояние высокого логического уровня и, таким образом, задают этот режим по умолчанию, если выходы не имеют внешних подключений. На Рис. 13 изображена временная диаграмма для данного режима.

В Табл. 10 содержится более подробная

информация для величин, приведенных на Рис. 13. Для FPGA,

соединенных в цепочку, процесс конфигурирования должен быть задержан до тех

пор, пока на контактах ![]() всех

микросхем цепочки не появится высокий логический уровень.

всех

микросхем цепочки не появится высокий логический уровень.

Таблица 10. Параметры сигналов подчиненного и ведущего режимов

Параметр |

Обозначение | Значение | ||

| min | max | |||

| Предустановка/удержание входного сигнала DIN, подчиненный режим | 1/2* |

|

5.0 нс/0 нс | |

| Предустановка/удержание входного сигнала DIN, ведущий режим | 1/2* |

|

5.0 нс/0 нс | |

| Задержка сигнала DOUT | 3* |

|

12 нс | |

| Длительность высокого уровня | 4* |

|

5.0 нс | |

| Длительность низкого уровня | 5* |

|

5.0 нс | |

| Частота |

|

66 МГц | ||

| *См. рис. 13. | ||||

6.1.2. Ведущий последовательный резким

В ведущем последовательном режиме с выхода CCLK FPGA сигнал подается на соответствующий вход микросхемы ППЗУ, которая передает данные на DIN-вход той же микросхемы FPGA. Прием данных в FPGA осуществляется по каждому нарастающему фронту сигнала CCLK. После полного конфигурирования микросхемы, данные для следующих устройств, соединенных цепочкой, появляются на выходе DOUT после каждого нарастающего фронта сигнала CCLK. Данные конфигурирования, поступающие на все микросхемы FPGA, соединенные в цепочку, обязательно начинаются с блока, называемого преамбулой.

Интерфейс, поддерживающий этот режим, идентичен интерфейсу подчиненного режима, за исключением того, что для генерации синхросигнала конфигурирования используется внутренний осциллятор FPGA. Частота для этого синхросигнала может быть выбрана из широкого диапазона значений, но по умолчанию всегда используется низкая частота. Переключение на более высокую частоту происходит данными, которые распознаются микросхемой в самом конфигурационном потоке, после чего оставшаяся часть потока загружается уже с новой скоростью. Переключение снова на более низкую частоту запрещается. Частота синхронизации CCLK устанавливается выбором ConfigRate в программе генерации конфигурационного потока. Максимальная частота CCLK, которая может быть выбрана — 60 МГц. Выбирая конкретную частоту CCLK, необходимо убедиться, что используемые ПЗУ и все соединенные в цепочку микросхемы FPGA рассчитаны на конфигурирование в таком темпе.

После включения питания, частота CCLK равна 2.5 МГц. Эта частота используется до момента загрузки битов ConfigRate, после чего частота меняется на новое значение, определенное этими битами. Если в проекте не задается другая частота, то используемая по умолчанию частота равна 4 МГц.

На Рис. 12 показана полная система,

содержащая кристалл в ведущем и кристалл в подчиненном режимах. В этой схеме

крайнее левое устройство работает в ведущем последовательном режиме. Остальные

устройства работают в подчиненном последовательном режиме. На вход ![]() микросхемы ППЗУ подается

сигнал с контактов

микросхемы ППЗУ подается

сигнал с контактов ![]() микросхемы FPGA.

Аналогично, на вход

микросхемы FPGA.

Аналогично, на вход ![]() — с выхода DONE.

При этом в зависимости от выбранной стартовой последовательности существует

конфликт потенциалов на контакте DONE.

— с выхода DONE.

При этом в зависимости от выбранной стартовой последовательности существует

конфликт потенциалов на контакте DONE.

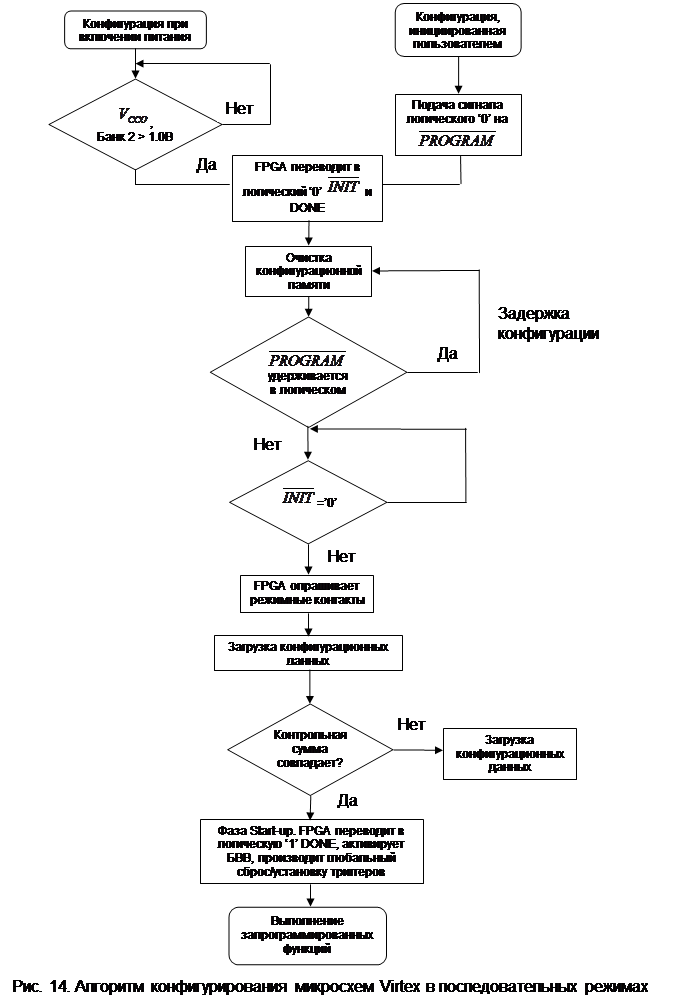

Для последовательного конфигурирования микросхем FPGA необходимо использовать последовательность, изображенную в виде алгоритма на Рис. 14.

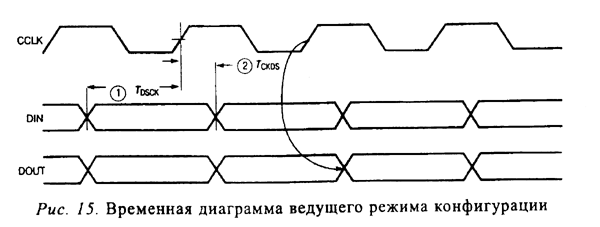

Временная диаграмма для ведущего последовательного режима показана на Рис. 15. Данный режим выбирается заданием кода <000> или <100> на входах М2, Ml, М0. Необходимую временную информацию для этого режима содержит Табл. 10.

Время нарастания напряжения питания ![]() от уровня 1 В до минимально

допустимого значения

от уровня 1 В до минимально

допустимого значения ![]() не должно

превышать 50 мс, в противном случае необходимо удерживать сигнал

не должно

превышать 50 мс, в противном случае необходимо удерживать сигнал ![]() в состоянии низкого

логического уровня до момента достижения допустимого уровня

в состоянии низкого

логического уровня до момента достижения допустимого уровня ![]() .

.

6.1.3. Режим SelectMAP

SelectMAP — самый быстрый режим конфигурирования. В этом режиме данные записываются в FPGA побайтно с использованием флага BUSY, управляющего потоком данных.

Внешний источник создаёт байтовый поток данных

и сигналы CCLK, выбор кристалла (Chip

Select — ![]() ),

запись (

),

запись (![]() ). Если установлен высокий

логический уровень сигнала BUSY,

данные должны удерживаться до тех пор, пока BUSY не

будет переведен в состояние низкого уровня.

). Если установлен высокий

логический уровень сигнала BUSY,

данные должны удерживаться до тех пор, пока BUSY не

будет переведен в состояние низкого уровня.

Используя этот режим можно считать данные.

Если сигнал ![]() не установлен (т.е.

находится в состоянии высокого логического уровня), конфигурационные данные

читаются обратно из FPGA, как часть операции

обратного считывания.

не установлен (т.е.

находится в состоянии высокого логического уровня), конфигурационные данные

читаются обратно из FPGA, как часть операции

обратного считывания.

После окончания конфигурирования контакты порта SelectMAP могут использоваться как дополнительные пользовательские входы-выходы.

Можно использовать этот порт для быстрого 8-битового обратного считывания конфигурационных данных.

Сохранение такой возможности после конфигурирования реализуется на этапе создания битового потока. Для сохранения такой возможности необходимо использовать ограничения типа PROHIBIT, предохраняющие контакты порта SelectMAP от использования в качестве пользовательских.

Несколько FPGA

Virtex могут конфигурироваться в режиме SelectMAP, и

далее одновременно запускаться для штатного функционирования. Для конфигурирования

нескольких устройств таким способом, необходимо соединить параллельно индивидуальные

сигналы отдельных микросхем CCLK, Data, ![]() и BUSY.

Конкретные микросхемы конфигурируются по очереди за счет поочередной подачи

активного сигнала на контакт выборки (

и BUSY.

Конкретные микросхемы конфигурируются по очереди за счет поочередной подачи

активного сигнала на контакт выборки (![]() )

этой FPGA и записи соответствующих ей

данных. В Табл. 11 представлены временные параметры сигналов режима SelectMAP.

)

этой FPGA и записи соответствующих ей

данных. В Табл. 11 представлены временные параметры сигналов режима SelectMAP.

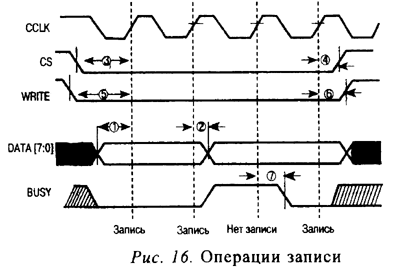

Запись

Процедура записи посылает пакеты

конфигурационных данных в FPGA.

Необходимо отметить, что конфигурационный пакет можно расщепить на несколько

таких последовательностей. Пакет не должен быть закончен за время одной

активизации сигнала ![]() , изображенной на Рис.

16.

, изображенной на Рис.

16.

Последовательность операций:

1. Установить сигналы ![]() и

и ![]() в состояние низкого

логического уровня. Отметим, что если сигнал

в состояние низкого

логического уровня. Отметим, что если сигнал ![]() активизируется

во время уже функционирующего сигнала CCLK,

сигнал

активизируется

во время уже функционирующего сигнала CCLK,

сигнал ![]() должен оставаться

неизменным. В противном случае, как описано далее, будет инициировано

преждевременное прекращение процедуры.

должен оставаться

неизменным. В противном случае, как описано далее, будет инициировано

преждевременное прекращение процедуры.

Таблица 11. Параметры сигналов режима SelectMAP.

Параметр |

Обозначение | Значение | ||

| min | max | |||

| Предустановка/удержание входных сигналов D0-D7 | 1/2* |

|

5.0 нс/0 нс | |

|

Предустановка/удержание входного

сигнала |

3/4* |

|

7.0 нс/0 нс | |

|

Предустановка/удержание входного

сигнала |

5/6* |

|

7.0 нс/0 нс | |

|

Задержка

распространения сигнала |

7* |

|

12.0 нс | |

| Частота |

|

66 МГц | ||

| Частота без подтверждения получения данных |

|

50 МГц | ||

| *См. рис. 16. | ||||

2. Данные подать на вход D[7:0].

Отметим, что для избежания конфликта между данными от различных источников,

информация не должна выдаваться во время, когда сигнал ![]() имеет значение ‘0’, a

имеет значение ‘0’, a

![]() — значение ‘1’. Также

нельзя активизировать больше одного CS, в

то время когда сигнал WRITE

имеет значение ‘1’.

— значение ‘1’. Также

нельзя активизировать больше одного CS, в

то время когда сигнал WRITE

имеет значение ‘1’.

3. Данные принимаются по нарастающему фронту CCLK при условии, что сигнал BUSY при этом имеет значение ‘0’. В случае, если сигнал BUSY имел значение ‘1’ от предыдущей записи, данные не принимаются. Данные снова будут приниматься по первому же нарастающему фронту CCLK после перехода BUSY в состояние ‘0’; при этом данные должны удерживаться до этого события.

4. Повторять шаги 2 и 3 до тех пор, пока не будут переданы все данные.

5. Перевести сигналы ![]() и

и ![]() в неактивное состояние.

в неактивное состояние.

Алгоритм процедуры записи показан на Рис.

17. Отметим, что если сигнал CCLK

медленнее, чем ![]() , FPGA не

будет выставлять сигнал BUSY, в

этом случае обмен подтверждениями готовности после реального приема данных не

нужен, и данные могут просто вводиться в FPGA по

каждому циклу сигнала CCLK.

, FPGA не

будет выставлять сигнал BUSY, в

этом случае обмен подтверждениями готовности после реального приема данных не

нужен, и данные могут просто вводиться в FPGA по

каждому циклу сигнала CCLK.

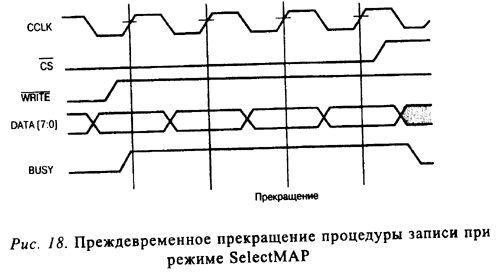

Преждевременное прекращение процедуры

После установки активного уровня сигнала ![]() , пользователь не может

переключаться с записи на чтение или наоборот. В противном случае такое

действие приведет к преждевременному прекращению текущей пакетной команды.

Устройство будет оставаться в состоянии BUSY

(занято) до тех пор, пока прерванная процедура будет завершена. После

прекращения процедуры, для продолжения приема пакета, необходимо повторить передачу

того слова, которое было прервано не на границе слова.

, пользователь не может

переключаться с записи на чтение или наоборот. В противном случае такое

действие приведет к преждевременному прекращению текущей пакетной команды.

Устройство будет оставаться в состоянии BUSY

(занято) до тех пор, пока прерванная процедура будет завершена. После

прекращения процедуры, для продолжения приема пакета, необходимо повторить передачу

того слова, которое было прервано не на границе слова.

Для того чтобы инициировать преждевременное

прекращение процедуры записи, необходимо перевести сигнал ![]() в неактивное состояние.

Как показано на Рис. 18, прекращение процедуры начнется с приходом

нарастающего фронта CCLK.

в неактивное состояние.

Как показано на Рис. 18, прекращение процедуры начнется с приходом

нарастающего фронта CCLK.

6.1.4. Использование резкима периферийного сканирования для конфигурирования Virtex

Для конфигурирования в режиме периферийного сканирования используются только специальные контакты порта тестового доступа (Test Access Port — ТАР) в соответствии со стандартом IEEE 1149.1.

Конфигурирование через порт ТАР выполняется с помощью специальной команды CFG_IN. Эта команда позволяет преобразовать входные данные, поступающие на вход TDI, в пакет данных для внутренней шины конфигурирования.

Для конфигурирования FPGA через порт периферийного сканирования необходимо выполнить следующие действия:

1. Загрузить команду CFG_IN во внутренний регистр команд (instruction register — IR).