Реферат: Микроконтроллеры Z86 фирмы ZILOG

Реферат: Микроконтроллеры Z86 фирмы ZILOG

Рис. 1.26. Регистр маски прерываний IMR

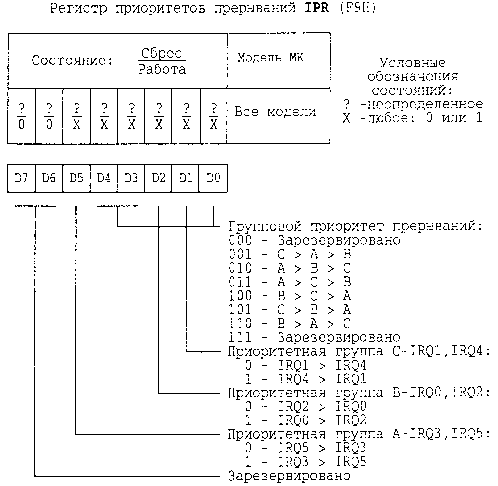

Регистр приоритета прерываний IPR (рис.1.27) позволяет устанавливать любое соотношение приоритетов как между группами прерываний А, В, С, так и между отдельными запросами прерываний внутри группы. В каждую группу включено по два запроса.

МК Z8 поддерживает как процесс векторных прерываний, так и процесс поллинга.

Рис. 1.27. Регистр приоритетов прерываний IMR

В случае векторного процесса каждый уровень прерывания имеет собственный вектор —адрес подпрограммы обслуживания этого уровня прерывания. Векторы прерываний размещены в начальной зоне ПЗУ (см. рис. 1.3). Инициализация процесса векторного прерывания происходит, если прерывания глобально разрешены и есть хотя бы один незамаскированный запрос прерывания. Если таких запросов несколько, то выбирается вектор прерывания с наивысшим приоритетом. Далее реализуется следующая последовательность действий:

— загружается в стек младший байт PC;

— загружается в стек старший байт PC;

—загружается в стек регистр флагов FLAGS;

— читается старший байт вектора;

— читается младший байт вектора;

—вектор загружается в PC.

Эта последовательность занимает 24 такта синхронизации TpC. Наихудшее время реакции на прерывание можно вычислить, прибавив к этому времени 2TpC для синхронизации внешнего запроса прерывания и время выполнения самой длинной команды в прерываемой программе.

1.3. Система команд микроконтроллеров Z8

Математические возможности МК характеризуются системой команд. В МК использован двухадресный принцип построения команд, что позволяет сократить количество требуемых пересылок операндов. Первый операнд после выполнения команды становится результатом и называется операндом-получателем ( Destination Operand ), а второй —сохраняет свое значение и называется операндом-источником ( Source Operand ). Первый в описании системы команд обозначен аббревиатурой dst, а второй —src.

Код любой команды МК содержит код операции (КОП), определяющий операцию команды, и до двух адресных полей. Способы трактовки кодов в адресном поле называются способами адресации операндов.Прежде чем рассматривать набор команд, необходимо более подробно рассмотреть используемые способы адресации операндов.

1.3.1. Способы адресации операндов

В МК Z8 использовано шесть основных способов адресации операндов :

— регистровая ( Register );

— косвенная регистровая ( Indirect Register );

— индексная ( Indexed );

— прямая ( Direct );

— относительная ( Relative );

— непосредственная ( Immediate ).

Кроме того, регистровая и косвенная регистровая адресации имеют ряд модификаций: они могут использовать сокращенный 4-битный адрес рабочего регистра, полный 8-битный адрес регистра, сокращенный 4-битный адрес рабочей пары регистров, полный 8-битный адрес регистровой пары. При адресации пар регистров используется четное выравнивание, т.е. допустимые адреса —четные числа. Шестнадцатибитные операнды занимают в регистровом файле пару регистров, причем по четному адресу размещается старший байт.

Все способы адресации операндов в системе команд МК Z8 приведены в табл.1.7. В таблице указаны условные обозначения способов адресации, используемые в дальнейшем в таблице команд, наименование способа адресации, обозначение операнда на языке ассемблера, диапазон значений адреса и номер рисунка, на котором дана графическая интерпретация способа адресации.

Следует отметить, что адреса типа R, RR, IR, IRR предполагают использование как полного 8-битного адреса регистра, так и сокращенного 4-битного. В последнем случае адрес размещается в младшей тетраде адресного байта, а в старшей тетраде указывается код 1110B (EH) :

| E | Dst/src |

Поэтому обращение к регистрам рабочей группы E СРФ возможно только с помощью рабочей регистровой адресации (см. п.п.1.2.2.1).

Таблица 1.7. Способы адресации операндов

| Способ | Наименование | Операнд | Диапазон | Рис. |

| r | Рабочая регистровая(РР) | Rn | n=0,...,15 | 1.35 |

| R | Регистровая или РР |

Reg Rn |

00H —FFH n=0,...,15 |

1.36 1.35 |

| RR | Регистровая пара или PP пара (четное выравнивание) |

Reg RRp |

00H —FEH p=0,...,14 |

1.38 1.37 |

| Ir | Косвенная РР | @Rn | n=0,...,15 | 1.39 |

| IR | Косвенная регистровая или косвенная РР |

@Reg @Rn |

00H —FFH n=0,...,15 |

1.40 1.39 |

| Irr | Косвенная через РР пару | @RRp | p=0,...,14 | 1.41 |

| IRR | Косвенная через регистровую пару или РР пару |

@Reg @RRp |

00H —FEH p=0,...,14 |

1.42 1.41 |

| X | Индексная | Reg(Rn) | 00H —FFH | 1.43 |

| DA | Прямая | Addrs | 0H —FFFFH | 1.44 |

| RA | Относительная | Addr | -128- +127 | 1.45 |

| IM | Непосредственная | #Data | 00H —FFH | 1.46 |

1.3.2. Флаги процессора

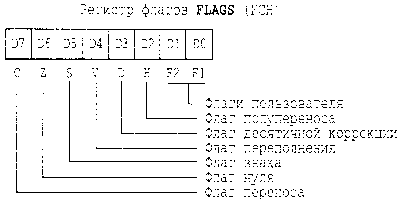

Флаговый регистр FLAGS (FCH) содержит информацию о текущем состоянии процессора. Флаги и их расположение в регистре приведены на рис.1.47. Состояние флагового регистра после сброса является неопределенным.

Рис. 1.47. Регистр флагов FLAGS

Флаговый регистр FLAGS содержит 6 флагов состояния, информация в которых устанавливается в результате работы процессора. Четыре флага (C, V, Z, S) используются командами условного перехода. Два флага (H и D) используются командой десятичной коррекции. Оставшиеся два бита могут быть использованы как флаги пользователя (F1 и F2). Ниже подробно рассмотрено назначение каждого из основных флагов МК Z8.

1.3.2.1. Флаг переноса C (Carry Flag)

Флаг переноса устанавливается в 1, если в результате арифметической операции генерируется “перенос из” или “заем в” старший 7-ой бит результата. В противном случае флаг С очищается в 0.

В процессе выполнения команд циклического или арифметического сдвига флаг переноса С содержит последний бит, выдвинутый из указанного в команде регистра.

Команды могут устанавливать, сбрасывать или инвертировать (дополнять) флаг переноса.

1.3.2.2. Флаг нуля Z (Zero Flag)

Если в результате арифметической или логической операции получается нулевой результат, то флаг Z устанавливается в 1, в противном случае флаг Z очищается в 0.

Если результат команды проверки бита в регистре равен 00Н,0то флаг нуля устанавливается в 1, в противном случае — очищается в 0.

Если результат выполнения команды циклического или арифметического сдвига равен 00Н, флаг Z устанавливается в 1, иначе —сбрасывается в 0.

1.3.2.3. Флаг знака S (Sign Flag)

Флаг знака хранит значение старшего бита результата текущей арифметической или логической операции, операции циклического илиарифметического сдвига.

Для производства арифметических операций над числами со знаком в МК используется представление информации в дополнительном коде. Положительное число при этом идентифицируется в старшем значащем разряде и, соответственно, значение флага знака также равно 0. Отрицательное число идентифицируется 1 в старшем значащем разряде и, соответственно, флаг S также будет равен 1.

1.3.2.4. Флаг переполнения V (Overflow Flag)

Для знаковых арифметических операций, операций циклического и арифметического сдвигов флаг переполнения V устанавливается в 1, если результат больше максимально возможного положительного числа (+127) или меньше минимально возможного отрицательного числа (-128), представленного 8-битным дополнительным кодом. Флаг V устанавливается в 0, если переполнение отсутствует. В результате поразрядных логических операций флаг V всегда сбрасывается в 0.

1.3.2.5. Флаг десятичной коррекции D (Decimal Adjust Flag)

Флаг десятичной коррекции D используется для двоично-десятичной арифметики BCD (Binary Coded Decimal). Поскольку алгоритм десятичной коррекции различен для сложения и вычитания, этот флаг сохраняет информацию о последней выполненной команде, для последующей команды десятичной коррекции DA. После выполнения операциивычитания флаг D устанавливается в 1, а после операции сложения —очищается в 0.

1.3.2.6. Флаг полупереноса H (Half Carry Flag)

Флаг полупереноса H устанавливается в 1, когда при сложениичисел генерируется перенос из 3-его бита или при вычитании генерируется заем в 3-ий бит. Флаг H используется командой десятичной коррекции DA.

Значения всех флагов изменяются командой IRET при восстановлении из стека состояния флагового регистра. Команды WDH и WDT устанавливают флаги Z, S и V в неопределенное состояние. Команда SWAP устанавливает в неопределенное состояние флаги C и V.

1.3.3. Набор команд

Команды микроконтроллеров Z8 функционально могут быть разделены на восемь групп:

— команды загрузки;

— арифметические команды;

— логические команды;

— команды управления программой;

— команды манипуляции битами;

— команды пересылки блоков;

— команды сдвигов;

— команды управления процессором.

1.3.3.1. Описание системы команд

В табл.1.8 приведено краткое описание системы команд микроконтроллеров, причем для каждой команды дано мнемоническое обозначение, принятое в языке ассемблера, указан состав операндов и смысл команды на английском языке ( для понимания происхождения мнемоники как аббревиатуры ) и на русском языке. Аббревиатура “сс” в колонке операндов команд управления программой означает код условия ( condition ), а аббревиатура “r”— любой регистр из рабочей группы ( register ).

Таблица 1.8. Краткое описание системы команд микроконтроллера Z8

| Мнемоника | Операнды | Наименование команды | |||||

| Английский язык | Русский язык | ||||||

| КОМАНДЫ ЗАГРУЗКИ | |||||||

|

CLR LD LDC LDE POP PUSH |

dst dst,src dst,src dst,src dst src |

Clear Load Load Constant Load External Data Pop Push |

Очистить Загрузить Загрузить константу Загрузить внешние данные Извлечь из стека Загрузить в стек |

||||

| АРИФМЕТИЧЕСКИЕ КОМАНДЫ | |||||||

|

ADC ADD CP DA DEC DECW INC INCW SBC SUB |

dst,src dst,src dst,src dst dst dst dst dst dst,src dst,src |

Add with Carry Add Compare Decimal Adjust Decrement Decrement Word Increment Increment Word Subtract with Carry Subtract |

Сложить с переносом Сложить Сравнить Десятичная коррекция Декремент Декремент слова Инкремент Инкремент слова Вычесть с заемом Вычесть |

||||

| ЛОГИЧЕСКИЕ КОМАНДЫ | |||||||

|

AND COM OR XOR |

dst,src dst dst,src dst,src |

Logical AND Complement Logical OR Logical EXCLUSIVE OR |

Логическое И Дополнение ( НЕ ) Логическое ИЛИ Исключающее ИЛИ |

||||

| КОМАНДЫ УПРАВЛЕНИЯ ПРОГРАММОЙ | |||||||

|

CALL DJNZ IRET JP JR RET |

dst r,dst cc,dst cc,dst |

Call Procedure Decrement and Jump Non Zero Interrupt Return Jump Jump Relative Return |

Вызов подпрограммы Декремент и переход, если не нуль Возврат из прерывания Переход Переход относительный Возврат из подпрограммы |

||||

| КОМАНДЫ МАНИПУЛЯЦИИ БИТАМИ | |||||||

|

TCM TM AND OR XOR |

dst,src dst,src dst,src dst,src dst,src |

Test Complement Under Mask Test Under Mask Bit Clear Bit Set Bit Complement |

Проверить дополнение с маской Проверить с маской Очистить биты Установить биты Дополнить биты |

||||

| КОМАНДЫ ПЕРЕСЫЛКИ БЛОКОВ | |||||||

|

LDCI LDEI |

dst,src dst,src |

Load Constant Autoincrement Load External Data Autoincrement |

Загрузить константу с автоинкрементом Загрузить внешние данные с автоинкрементом |

||||

| КОМАНДЫ СДВИГОВ | |||||||

|

RL RLC RR RRC SRA SWAP |

dst dst dst dst dst dst |

Rotate Left Rotate Left Through Carry Rotate Right Rotate Right Through Carry Shift Right Arithmetic Swap Nibbles |

Циклический влево Циклический влево через перенос Циклический вправо Циклический вправо через перенос Арифметический вправо Свопинг полубайтов |

||||

| КОМАНДЫ УПРАВЛЕНИЯ ПРОЦЕССОРОМ | |||||||

|

CCF DI EI HALT NOP RCF SCF SRP STOP WDH WDT |

src |

Complement Carry Flag Disable Interrupts Enable Interrupts Halt No Operation Reset Carry Flag Set Carry Flag Set Register Pointer Stop WDT Enable During HALT WDT Enable or Refresh |

Дополнить флаг переноса Запретить прерывания Разрешить прерывания Переход в режим HALT Нет операции Сбросить флаг переноса Установить флаг переноса Установить указатель регистров Переход в режим STOP Разрешение сторожевого таймера в режиме HALT Разрешение или переза- пись сторожевого таймера |

||||

1.3.3.2. Условия ветвления программы

Команды переходов JP и JR обеспечивают ветвление программы по различным условиям. В качестве условий используются состояния флагов C,Z,S и V, а также их логические функции. Набор допустимых для языка ассемблера условий с указанием мнемонического обозначения (cc), значения, соответствующего состояния флагов и шестнадцатеричного кода условия приведен в табл.1.9. Набор условий предусматривает ветвление по состояниям отдельных флагов, а также по всем возможным соотношениям между целыми числами со знаком и между беззнаковыми целыми числами.

Таблица 1.9. Мнемоника условий (cc) и цифра КОП (c)

| cc | Значение | Состояние флагов | c |

| F | Всегда ложно | — | 0 |

| Всегда истинно | — | 8 | |

| C | Есть перенос | C=1 | 7 |

| NC | Нет переноса | C=0 | F |

| Z | Есть нуль | Z=1 | 6 |

| NZ | Нет нуля | Z=0 | E |

| PL | Положительно | S=0 | D |

| MI | Отрицательно | S=1 | 5 |

| OV | Переполнение | V=1 | 4 |

| NOV | Нет переполнения | V=0 | C |

| EQ | Равно | Z=1 | 6 |

| NE | Не равно | Z=0 | E |

| GE | Больше или равно | (S xor V)=0 | 9 |

| LT | Меньше | (S xor V)=1 | 1 |

| GT | Больше | (Z or (S xor V))=0 | A |

| LE | Меньше или равно | (Z or (S xor V))=1 | 2 |

| UGE | Б/з больше или равно | C=0 | F |

| ULT | Б/з меньше | C=1 | 7 |

| UGT | Б/з больше | (C=0 and Z=0)=1 | B |

| ULE | Б/з меньше или равно | (C or Z)=1 | 3 |

1.4. Конструктивное исполнение микроконтроллеров Z8

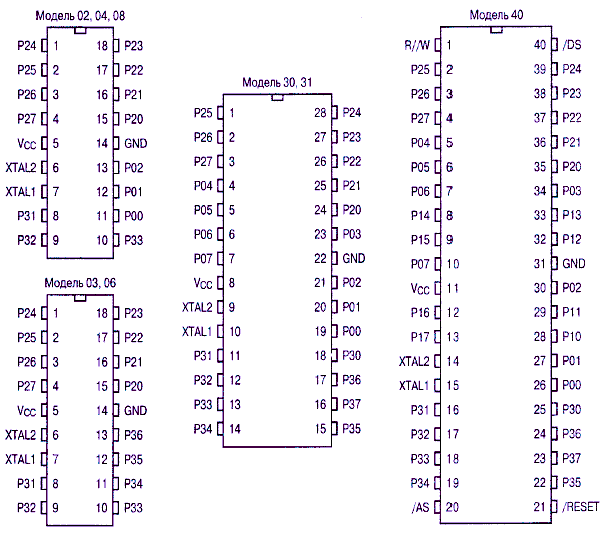

Микроконтроллеры широкого применения Z8 выпускаются в различном конструктивном исполнении. Наиболее дешевым и удобным для большинства применений является корпус типа DIP ( Dual In Line Package ). Схема расположения выводов МК для корпусов этого типа показана на рис.1.48.

Большинство моделей МК имеет также вариант исполнения в корпусе типа SOIC ( Smal Outline Package ), предназначенном для монтажа на поверхность. Модель 40 выпускается также и в квадратных 44 выводных корпусах типа PLCC ( Plastic Chip Carrier ) и QFP (Quad Flat Pack ). Модели МК 30, 31, и 40 с возможностью многократного перепрограммирования производятся в корпусах типа CerDIP Window Lid, имеющих кварцевое окно для оптического стирания.

Полное обозначение микросхемы, кроме шифра, указанного в табл.1.1, содержит дополнительно две цифры, соответствующие максимальной частоте в мегагерцах, три буквы и необязательный буквенно-цифровой код партии. Первая буква означает тип корпуса ( P —пластмассовый DIP, S- SOIC и т.п. ), вторая —температурный диапазон ( S —стандартный: 0 —700C, E -расширенный: -40 —1050C), третья —характеризует защитную оболочку от воздействия окружающей среды ( C — стандартная пластмассовая, E —стандартная герметичная ).

Например, полное обозначение МК Z86E02 может быть следующим:

Z86E0208PSC.

Рис. 1.48. Расположение выводов микроконтроллеров Z8

Для более полной информации следует обратиться к фирменным справочникам [4,5].

ЗАКЛЮЧЕНИЕ

На основе рассмотренных в настоящем пособии материалов можно заключить, что однокристальные микроконтроллеры являются перспективной элементной базой для построения устройств передачи и обработки данных. Они имеют все необходимые атрибуты для решения всех задач, возникающих при проектировании таких устройств. Прежде всего, это аппаратные средства микроконтроллеров, начиная от встроенной памяти программ и данных и кончая размещенными на кристалле периферийными устройствами, а также средствами обеспечения надежной работы в условиях помех. Разнообразие конструктивного исполнения и возможность выбора варианта с низким напряжением питания и жесткими условиями эксплуатации позволяют разработчику всегда подобрать подходящую модель микроконтроллера для своей конкретной задачи. Комплексная система команд, возможность программирования аппаратной конфигурации, режимов резервирования и низкого электромагнитного излучения позволяют при весьма ограниченных объемах встроенной памяти программ решать сложнейшие задачи применения. Фирма Zilog снабжает свои изделия подробной документацией и средствами разработки.

Рассмотренными микроконтроллерами номенклатура продуктов фирмы для устройств передачи и обработки информации не ограничивается. Фирма Zilog производит большое разнообразие микроконтроллеров Z8, микроконтроллеров для цифрового телевидения, для телефонных автоответчиков, цифровых сигнальных процессоров, контроллеров для периферийных устройств и внешней памяти персональных компьютеров, аудио и мультимедиа приборов, специальных микропроцессоров для систем связи [7].

Использование микроконтроллеров для построения устройств передачи и обработки информации позволяет не только улучшить их основные технические характеристики, такие как надежность, быстродействие, точность, массогабаритные характеристики, энергопотребление, но и получить сопровождаемую конструкцию, совершенствование функций которой можно производить без изменения конструкторской документации и перестройки производственного цикла.