Реферат: Микроконтроллеры Z86 фирмы ZILOG

Реферат: Микроконтроллеры Z86 фирмы ZILOG

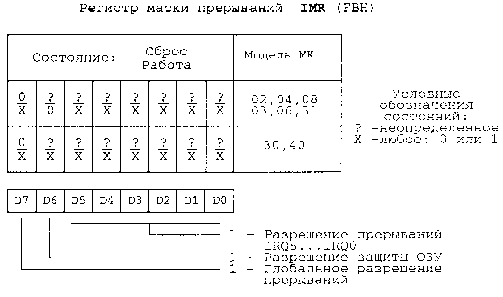

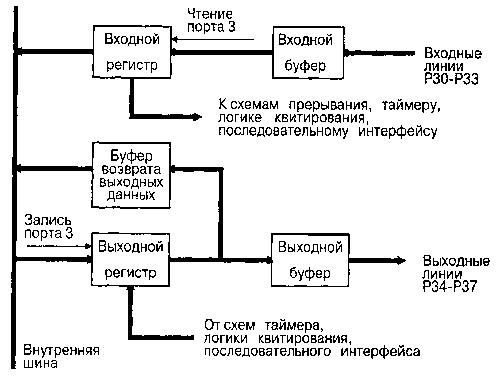

Рис. 1.10. Ввод с квитированием

| Состояние 1. | Вход RDY имеет высокий уровень, что указывает на готовность внешнего устройства к приему данных. | |

| Состояние 2. | МК записывает данные в регистр порта для инициализации передач данных. Запись в порт новых данных и переход выхода /DAV в состояние низкого уровня происходит только тогда, когда RDY имеет высокий уровень. | |

| Состояние 3. | Внешнее устройство делает уровень сигнала RDY низким после фиксации данных. Низкий уровень RDY вызывает генерирование запроса прерывания. МК может уже записать новые данные в ответ на низкий уровень DRY, однако эти данные не выводятся до состояния 5. | |

| Состояние 4. | Уровень выхода /DAV МК становится высоким в ответ на переход выхода RDY в состояние низкого уровня. | |

| Состояние 5. | Уровень выхода /DAV остается высоким, внешнее устройство может установить высокий уровень RDY, что возвращает интерфейс в его начальное состояние. |

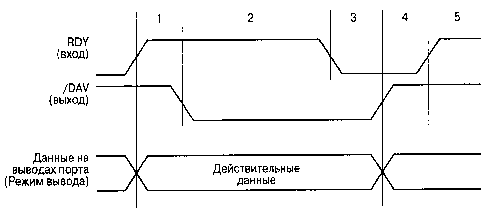

Рис. 1.11. Вывод с квитированием

Для приема и передачи сигналов квитирования используются соответствующие линии ввода/вывода порта Р3 (см. табл. на рис.1.9). Выбор направления обмена с квитированием осуществляется в соответствии с направлением, запрограммированным для старшей тетрады порта Р0 и для старшего бита порта Р2.

Режим стробируемого ввода/вывода реализуется как частный случай обмена с квитированием по схеме рис. 1.12.

Рис. 1.12. Стробируемый ввод/вывод

а) вывод; б) ввод.

Дополнительно к основным функциям порты P0 и P1 могут использоваться для интерфейса внешней памяти (Р0 -старшие разряды адреса A8...A15, P1 -мультиплексированная шина адреса/данных AD0...AD7), а порт P2 -для последовательного интерфейса SPI в модели 06 (P20 -вход DI, P27 -выход D0).

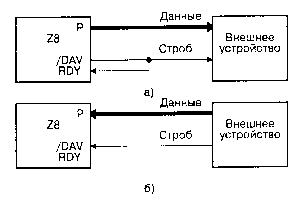

Схемотехника портов P0, P1, P2 поясняется рис. 1.13. Двухтактный буферный выходной усилитель выполнен на комплементарных МОП-транзисторах VT1 и VT2. Отключение транзистора VT1 переводит буферный усилитель в конфигурацию с открытым стоком. Входной буфер содержит автофиксатор и триггер Шмитта, который обеспечивает формирование входного сигнала.

Рис. 1.13. Схемотехника входного и выходного буферов

Автофиксатор предназначен для фиксации потенциала незадействованного входа на уровне допустимых КМОП потенциалов, близких к потенциалам шины питания VCC или общей шины GND. Этим исключается переход пары входных транзисторов в активный режим и резкое возрастание потребляемого тока. Автофиксатор представляет собой бистабильную ячейку (триггер), выполненную на двух замкнутых в кольцо инверторах, управляемую по выходу. Шунтирующее сопротивление автофиксатора -не менее 500 кОм. В ряде случаев, когда входы задействованы, шунтирующее действие автофиксатора нежелательно. Поэтому в некоторых модификациях МК предусмотрен специальный бит отключения автофиксаторов (Z86C30/31/40).

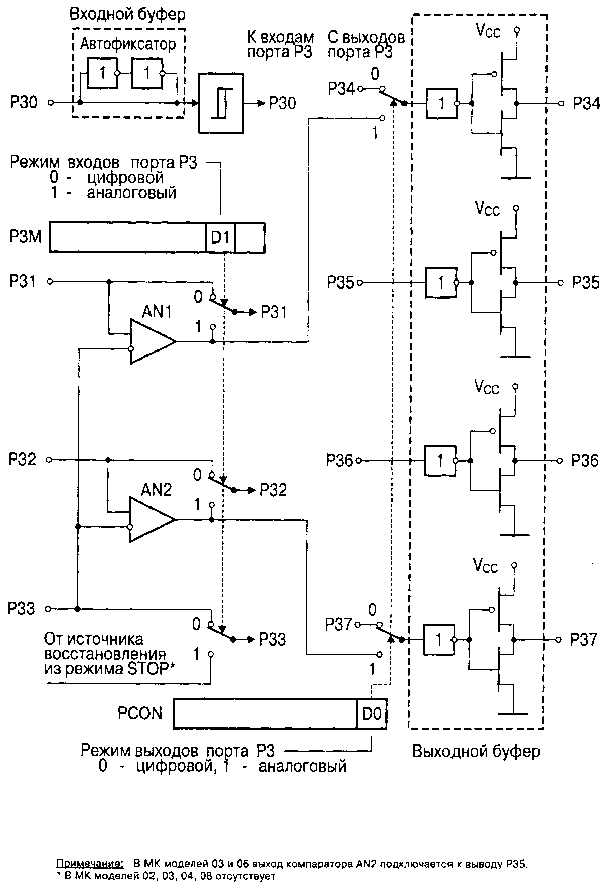

Порт Р3 -особый. Первые четыре его линии P30...P33 предназначены для ввода, вторые -P34...P37 -для вывода. Структурная схема порта и таблица назначения его выводов в различных режимах приведены на рис. 1.14. Независимо от выбранного режима с входами порта P3 связаны соответствующие запросы прерывания, указанные в таблице. Физическое наличие выводов порта P3 для разных моделей МК см. в табл. 1.2.

Рис. 1.14. Структурная схема порта P3

| Вывод P3 | Аналоговый режим | Квитирование | SPI | Таймеры | Внешняя память | Прерывания |

| P30 | IRQ3 | |||||

| P31 | AN1 | /DAV2/RDY2 | TIN | IRQ2 | ||

| P32 | AN2 | /DAV0/RDY0 | IRQ0 | |||

| P33 | REF | /DAV1/RDY1 | IRQ1 | |||

| P34 | AN1-OUT | RDY1/DAV1 | SK | /DM | ||

| P35 | AN2-OUT* | RDY0/DAV0 | /SS | |||

| P36 | RDY2/DAV2 | TOUT | ||||

| P37 | AN2-OUT |

Примечание: *только для моделей 03 и 06.

Порт P3 содержит четырехбитные входной и выходной регистры, входной и выходной буферы. Наличие четырехбитного буфера возврата позволяет при чтении порта P3 контролировать данные на выходных линиях. Запись информации в младшую тетраду порта P3 не имеет эффекта.

Схемотехника порта P3 иллюстрируется рис. 1.15. Дополнительной особенностью МК является наличие двух встроенных аналоговых компараторов AN1 и AN2, позволяющих решать вопросы сравнения аналоговых сигналов, квантования сигналов, аналого-цифрового преобразования. Входы и выходы порта P3 используются для обслуживания аналоговой схемы. Переключение входов в аналоговый режим осуществляется битом D1 регистра режима порта 3 PЗM, а выходов -битом D0 регистра управления портами PCON. Входы P31 и P32 используются соответственно для неинвертирующих входов компараторов, а вход P33 является входом опорного напряжения REF, общего для AN1 и AN2.

Рис. 1.15. Схемотехника порта P3

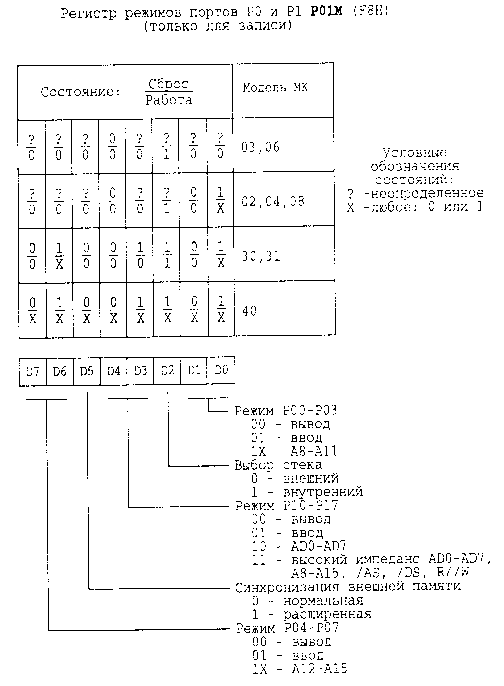

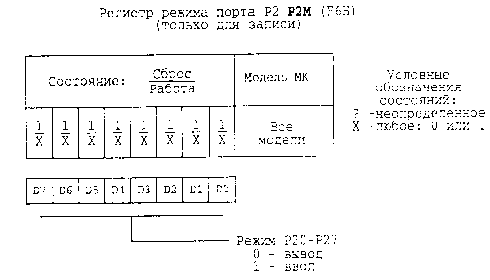

Управление работой портов реализуется путем записи информации в управляющие регистры: регистр режимов портов P0 и P1 -P01M, регистр режима порта P2 -P2M, регистр режима порта P3 -P3M. Все эти регистры находятся в рабочей группе F стандартного РФ. В моделях 03, 06, 30, 31 и 40, кроме того, для управления режимами работы выходных буферов портов (режим "открытый сток" и малошумящий режим) задействован регистр управления портами PCON, расположенный в расширенной группе регистров F. Все эти регистры предназначены только для записи. Результат чтения этих регистров будет равен FFH.

Назначение разрядов этих регистров и их состояние после сброса МК для разных моделей МК поясняется рис. 1.16 -1.19.

Рис. 1.16. Регистр режимов портов P0 и P1

Рис. 1.17. Регистр режима порта P2

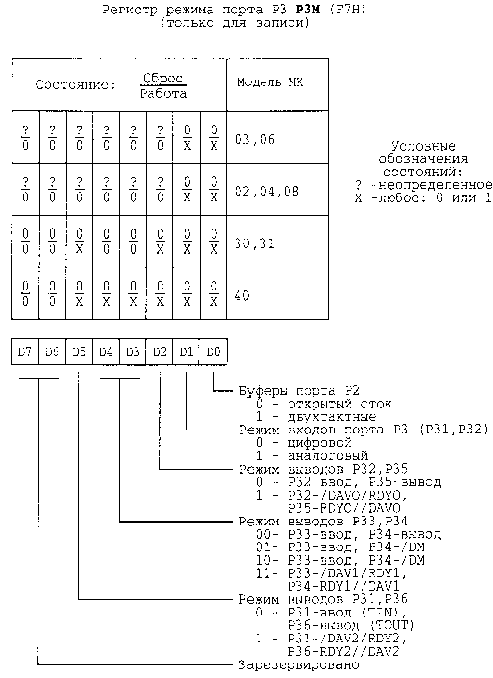

Рис. 1.18. Регистр режима порта P3

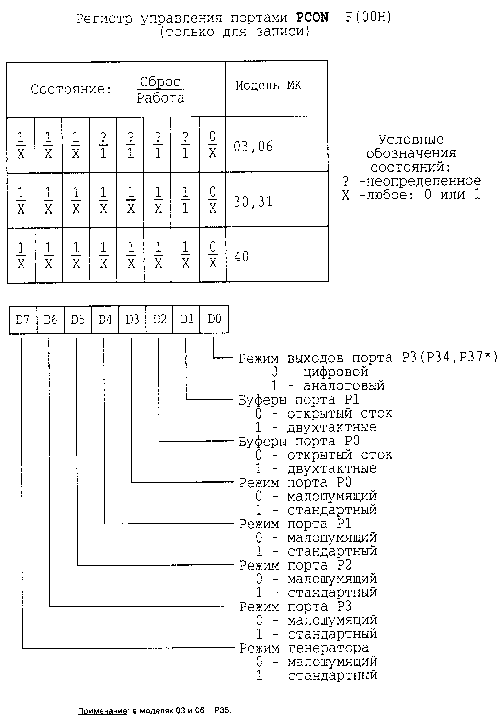

Рис. 1.19. Регистр управления портами PCON

Разрабатывая прикладную программу МК, необходимо предусматривать в ней процедуру инициализации портов ввода/вывода до выполнения операций обмена данными с внешними устройствами.

1.2.6. Таймеры/счетчики

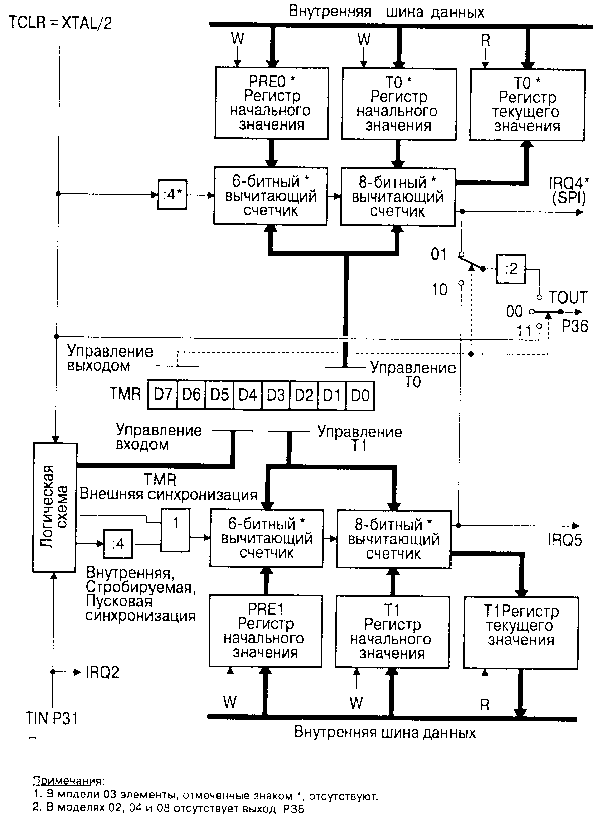

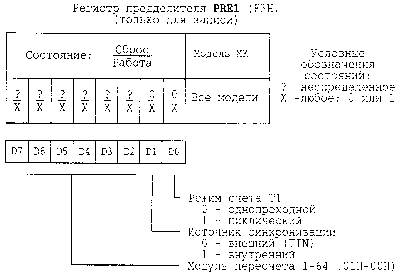

МК Z8 может иметь до двух таймеров/счетчиков, в зависимости от модели (см. табл.1.2). Каждый из 8-битных таймеров/счетчиков Т0 и Т1 снабжен 6-битным предделителем PRE0 и PRE1 (рис.1.20). Работа таймеров/счетчиков происходит независимо от работы процессора, что освобождает его от выполнения критичных временных операций, таких как счет событий, измерение временных интервалов, генерирование импульсов заданной длительности и т.п.

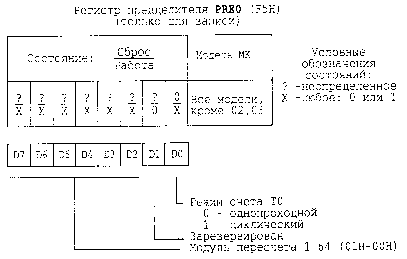

Рис. 1.20. Структурная схема таймеров/счетчиков

Каждый из таймеров/счетчиков может работать в однопроходном или циклическом режимах. В первом случае, при достижении таймером/счетчиком конца счета, счет прекращается, во втором —начальное значение перезагружается и счет продолжается. При управлении от внутренней синхронизации TCLK (TCLK = XTAL/2 в основном режиме работы генератора), ее частота дополнительно делится на 4. Этот делитель вместе с 6-битным предделителем и 8-битным таймером/счетчиком образуют синхронную 16-битную цепь. Таймер/счетчик T1 может также управляться с внешнего входа TIN, в качестве которого используется вывод Р31. Выходы таймеров/счетчиков и выход внутренней синхронизации могут быть с помощью программы скоммутированы на выход TOUT, в качестве которого используется вывод Р36. Управление работой таймеров/счетчиков осуществляется с помощью регистра режимов таймеров TMR. Регистры таймеров/счетчиков T0 и T1, предделителей PRE0 и PRE1, а также регистр TMR размещены в адресном пространстве СРФ, рабочая группа F ( см. рис.1.2). Поэтому для управления и контроля за работой таймеров/счетчиков никаких специальных команд не требуется. Каждый из предделителей PRE0 (F5H) и PRE1 (F3H) состоит из 8-битного регистра начального значения и 6-битного вычитающего счетчика (см. рис.1.20). Регистры предделителей предназначены только для записи, кроме начального значения содержат управляющие биты. Назначение разрядов этих регистров, их состояние после сброса и в процессе работы поясняется рис.1.21 и рис.1.22. Попытка чтения этих регистров дает результат FF. Начальное значение предделителей может быть в диапазоне от 1 до 64 ( 01H,...,3FH,00H ).

Каждый из таймеров/счетчиков (см. рис.1.20 ) T0 (F4H) иT1 (F2H) состоит из 8-битного вычитающего счетчика, регистра начального значения (только для записи) и регистра текущего значения (только для чтения). Начальное и текущее значения могут быть в диапазоне от 1 до 256 (01H,...,FFH,00H). После сброса состояние регистров T0 и T1 —неопределенное.

Рис. 1.21. Регистр предделителя PRE0

Рис. 1.22. Регистр предделителя PRE1

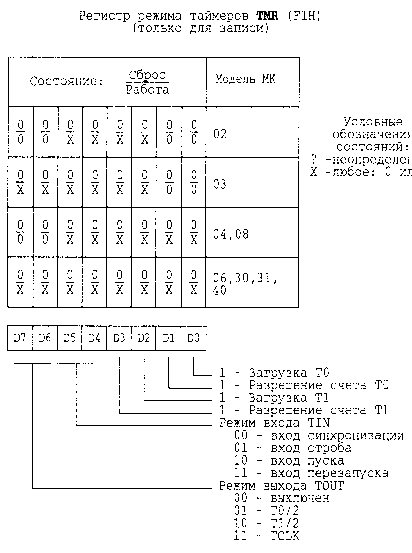

Регистр TMR содержит группы битов, управляющие загрузкой начальных значений, пуском/остановом таймеров, режимом входа TIN и режимом выхода TOUT. Назначение разрядов регистра TMR, состояние их после сброса и допустимые состояния в процессе работы для разных моделей МК показаны на рис.1.23.

Рис. 1.23. Регистр режимов таймеров TMR

Установка бита загрузки (D0 для T0 и D2 для T1) вызывает пересылку начального значения из регистров начального значения соответствующего предделителя и таймера в вычитающие счетчики. После загрузки эти управляющие биты сбрасываются. Новое значение может быть загружено в вычитающие счетчики в любое время. Если счетчики были запущены, то счет будет продолжаться с нового значения.

Таймеры/счетчики сохраняют свое состояние, пока бит разрешения счета (см. рис.1.23) равен 0. Для запуска таймеров/счетчиков соответствующий бит разрешения счета (D1 для T0 и D3 для T1) должен быть установлен в 1. Первый декремент будет иметь место через 4 периода внутренней синхронизации после установки программой бита разрешения счета или в следующем периоде внешней синхронизации (со входа TIN).

Биты загрузки и разрешения могут быть установлены одновременно. Например, с использованием команды

OR TMR,# 03H

можно загрузить и запустить таймер/счетчик T0.

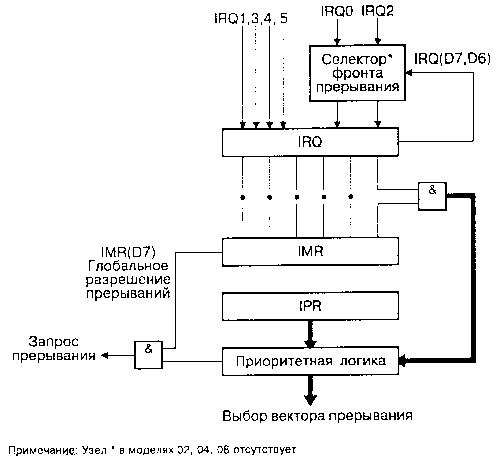

1.2.7. Прерывания

МК Z8 поддерживают 6-уровневую схему приоритетных прерываний от различных источников. Набор внешних источников прерывания связан со входами порта Р3 и инициирует запросы прерывания IRQ0,...,IRQ3 (см.табл. на рис.1.14). К внутренним источникам относятся таймеры/счетчики T0, T1 и последовательный интерфейс SPI. Им соответствуют запросы прерывания IRQ4, IRQ5. Обобщенная структурная схема организации прерываний и таблица соответствия источников показаны на рис.1.24. Следует отметить, что кроме аппаратной установки любой из запросов может быть установлен программным путем.

Аппаратные источники прерываний

| Запрос прерывания | Модель МК | ||||||||

| 02 | 03 | 06 | 04, 08 | 30, 31, 40 | |||||

| IRQ0 | P32 f | P32 s | P32 s | P32 f | P32 s | ||||

| IRQ1 | P33 f | P33 f | P33 f | P33 f | P33 f | ||||

| IRQ2 | P31 f | P31 s | P31 s | P31 f | P31 s | ||||

| IRQ3 | P32 f | SPI | P32 r | P30 f | |||||

| IRQ4 | T0 | T0 | T0 | ||||||

| IRQ5 | T1 | T1 | T1 | T1 | T1 | ||||

Рис. 1.24. Структурная схема организации прерываний

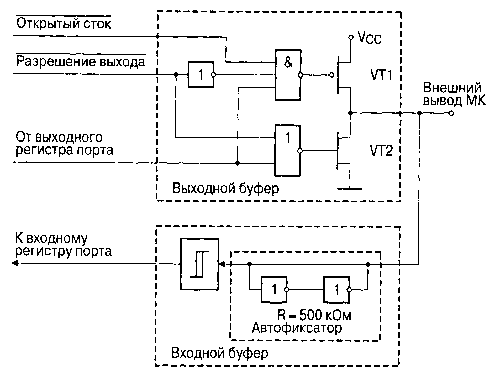

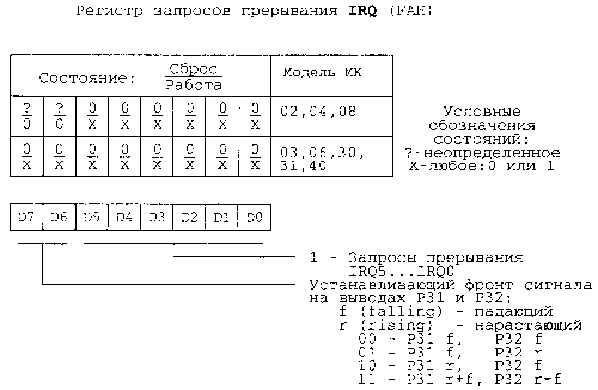

Схема управления прерываниями включает три управляющих регистра: регистр запросов прерывания IRQ, регистр маски прерывания IMR и регистр приоритетов прерывания IPR. Все регистры размещены в СРФ, рабочая группа F. Каждый внешний сигнал устанавливает в 1 соответствующий бит запроса в регистре IRQ (рис.1.25) при появлении фронта сигнала, указанного в таблице на рис.1.24. В моделях 03, 06, 30, 31 и 40 фронт сигнала, устанавливающий запросы IRQ0 и IRQ2, программируется путем записи информации в два старших бита регистра IRQ. Запросы прерываний от таймеров/счетчиков устанавливаются при достижении ими конца счета, а запрос от SPI —по завершении приема символа.

Рис. 1.25. Регистр запросов прерывания IRQ

Регистр маски прерываний IMR (рис.1.26) позволяет маскировать как каждое прерывание IRQ5 —IRQ0 отдельно (биты D5-D0), так и все прерывания глобально (бит D7). Последний бит устанавливается и сбрасывается особыми командами разрешения и запрещения прерываний EI и DI. Он автоматически сбрасывается при вызове подпрограммы обслуживания прерывания и автоматически устанавливается при выполнении команды возврата из подпрограммы обслуживания прерывания IRET. Следует отметить, что перед изменением содержимого IMR или IPR бит D7 регистра IMR должен быть сброшен.