Реферат: Микроконтроллеры Z86 фирмы ZILOG

Реферат: Микроконтроллеры Z86 фирмы ZILOG

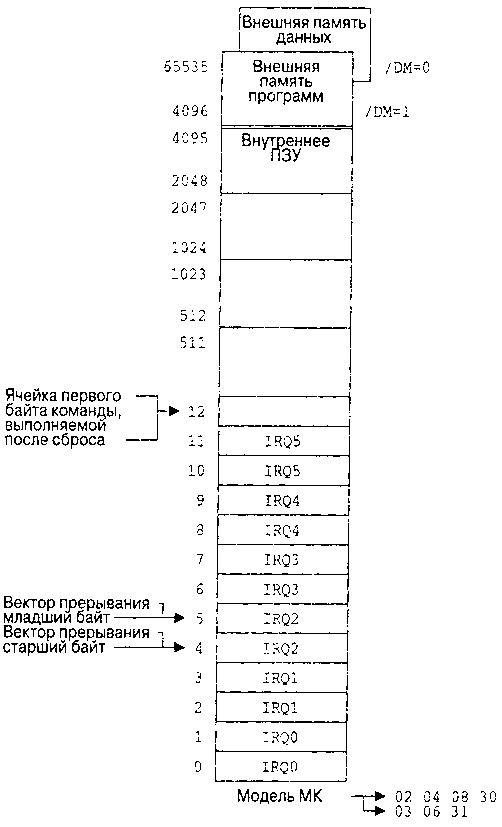

Рис. 1.3 Структура памяти

Внутреннее ПЗУ имеют все рассматриваемые модели МК. Модели с литерами C и L имеют масочное ПЗУ, а модели с литерой E -однократно -программируемое (One Time Programmable -OTP) ПЗУ. Размер внутреннего ПЗУ составляет для разных моделей МК от 512 байт до 4 Кбайт. Первые 12 байт зарезервированы для векторов прерываний (см. рис.1.3). Эти ячейки содержат 6 шестнадцатибитных векторов прерываний, которые соответствуют 6 возможным запросам прерывания: IRQ0 -IRQ5 (Interrupt Request). Начиная с ячейки 12 (0CH) размещается программа.

Модель 40 имеет возможность подключения внешней памяти программ объемом до 60 Кбайт. Такое подключение возможно с использованием мультиплексных линий адреса/данных (AD7 -AD0) порта 1 и адресных линий (A15 -A8) порта 0. Максимальный адрес внешней памяти программ -65535 (FFFFH). Этот интерфейс внешней памяти поддерживается управляющими линиями /AS, /DS и R//W. Доступ к памяти программ (в том числе и к внешней) осуществляется с помощью программного счетчика для считывания команд, а также командами загрузки констант LDC и LDCI.

Модель 40 также имеет возможность дополнительно адресовать до 60 Кбайт внешней памяти данных с адресами от 4096 (1000H) до 65535 (FFFFH) путем программирования выхода порта 3 P34 на выдачу сигнала /DM (Data Memory), позволяющего аппаратно разделить адресные пространства внешней памяти программ и внешней памяти данных. Обращение к внешней памяти данных осуществляется специальными командами загрузки LDE и LDEI, при исполнении которых сигнал /DM будет иметь активный низкий уровень.

В МК предусмотрен специальный бит защиты ПЗУ (ROM Protect), который программируется одновременно с внутренней памятью программ. Сущность защиты ПЗУ заключается в предотвращении "дампинга" содержимого ПЗУ. Эта функция в более ранних версиях МК реализована путем запрета команд LDC, LDCI, LDE и LDEI. При таком подходе защищенная программа не могла использовать эти команды, что не разрешало программисту реализовывать эффективные алгоритмы с просмотром таблиц. В последних версиях МК использование функции защиты ПЗУ никаких ограничений на программирование не накладывает.

1.2.2.3. Стек

Стек МК Z8 может располагаться во внутреннем ОЗУ или во внешней памяти данных. Размещение стека программируется путем записи бита D2 в регистр режима портов 0 и 1 -P01M. Запись 0 в этот бит задает внешний стек, 1 -внутренний. Такой выбор возможен только для модели 40, имеющей интерфейс внешней памяти, для остальных моделей бит D2 должен быть установлен в 1.

Расположение верхушки стека задается шестнадцатибитным указателем стека, размещенным в регистрах SPH и SPL стандартного регистрового файла. Для всех моделей, кроме модели 40, достаточно восьмибитного указателя стека (т.к. объем внутреннего ОЗУ не превышает 256 байт), и он размещается в регистре SPL. Регистр SPH с адресом FEH используется при этом как регистр общего назначения GPR. Указатель стека декрементируется перед операцией загрузки и инкрементируется после операции извлечения. Его содержимое -это всегда адрес верхушки стека.

Стек МК Z8 -это стек возврата из подпрограмм и прерываний, а также стек данных. При работе МК возможно переполнение стека вниз и вверх. Ответственность за недопустимость переполнения лежит на разработчике программы, иначе результат будет непредсказуем.

1.2.3. Синхронизация

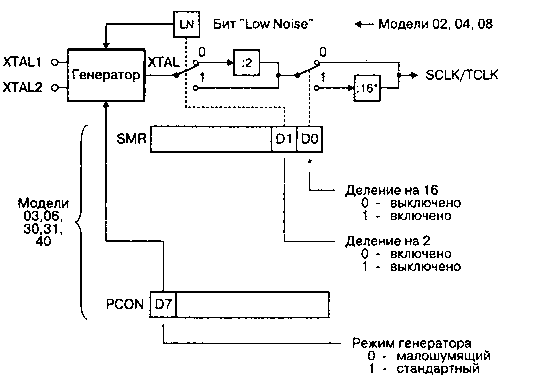

Обобщенная структурная схема синхронизации МК показана на рис 1.4.

Рис. 1.4 Структурная схема синхронизации

Схема состоит из задающего генератора, рассчитанного на подключение внешней времязадающей цепи или внешнего источника синхронизации, делителя частоты на 2 и делителя частоты на 16 (последний в моделях 02, 03, 04, 08 отсутствует). К входным контактам XTAL1 и XTAL2 (eXternal crysTAL) подключается времязадающая цепь, заставляющая генератор формировать синхроимпульсы с частотой XTAL. С выхода синхронизирующей схемы снимаются импульсы внутренней системной синхронизации SCLK (System CLocK) и синхронизации таймеров TCLK (Timer CLocK). Назначение делителя на 2 -формирование сигнала, а делитель на 16 предназначен для уменьшения рабочей частоты синхронизации и, соответственно, потребляемого тока, особенно в резервных режимах HALT и STOP.

Управление частотой в разных моделях МК осуществляется двумя способами. В моделях 02, 04, 08 управление сводится только к переводу схемы в малошумящий режим путем программирования (масочно или электрически) бита малошумящего режима Noise"(см. верхнюю часть рис.1.4.). При этом задающий генератор переводится в малошумящий режим и отключается делитель на 2. Максимальная частота работы генератора в этом режиме ограничивается 4 МГц и несколько снижается нагрузочная способность.

В моделях 03, 06, 30, 31 и 40 управление схемой синхронизации осуществляется путем записи управляющей информации в регистры PCON и SMR в процессе выполнения прикладной программы МК (см. нижнюю часть рис 1.4). Бит D7 регистра PCON управляет режимом задающего генератора, а биты D1 и D0 регистра SMR -делителями на 2 и на 16 соответственно. Логика управления показана на схеме.

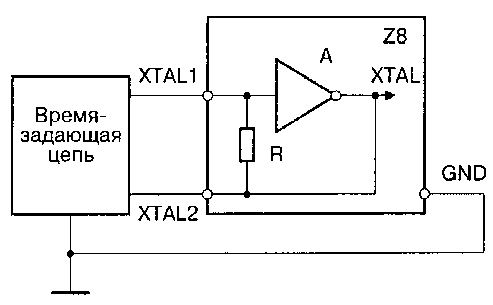

Схема задающего генератора показана на рис 1.5. Генератор построен на основе инвертирующего усилителя постоянного тока A с выполненной внутри кристалла резистивной обратной связью R. Схема генератора рассчитана на подключение внешней времязадающей цепи, являющейся гибкой обратной связью усилителя.

Рис. 1.5 Схема задающего генератора

Для устойчивого самовозбуждения генератора необходимо соблюдение условий баланса амплитуд и баланса фаз на частоте генерации. Условие баланса амплитуд заключается в равенстве 1 произведения коэффициента усиления усилителя на коэффициент передачи цепи обратной связи. Условие баланса фаз требует, чтобы суммарный сдвиг фаз в схеме был равен 0 (360о). Поскольку инвертирующий усилитель дает сдвиг фазы 180о, то цепь обратной связи должна обеспечивать фазовый сдвиг также на 180о.

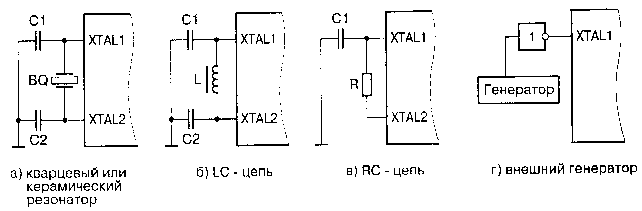

Этим условиям удовлетворяют схемы времязадающих цепей, показанные на рис.1.6. Генератор может работать с кварцевым или керамическим резонатором, LC -цепью, RC -цепью и внешним генератором. Работа генератора с RC -цепью требует определенной реконфигурации внутренней схемы, что достигается программированием (масочно или электрически) специального бита RC. Такую возможность имеют модели 03, 06, 30, 31, 40. Что касается моделей 02, 04, 08, то возможность запуска от RC - цепи имеют только самые последние версии этих моделей. Устойчивое возбуждение генератора возможно на частотах от 10 КГц до максимальной (см. табл.1.1.).

Рис. 1.6 Времязадающие цепи генератора

1.2.4. Сброс и сторожевой таймер

Функция сброса (Reset) необходима для инициализации важнейших элементов МК: схемы управления и синхронизации, программного счетчика (он устанавливается в состояние 000СН), управляющих регистров и портов (для определения их состояния после сброса для разных моделей МК, см. приложение 1).

Функция сброса активируется в следующих случаях:

- при подаче низкого уровня на вход /RESET (только для модели 40);

- при включении питания VСС;

- при переполнении сторожевого таймера WDT;

- при восстановлении из режима STOP.

В последнем случае (так называемый "теплый" старт) и в случае переполнения сторожевого таймера в режиме STOP порты и управляющие регистры не реинициализируются.

Функция сброса используется также для защиты памяти МК от падения напряжения питания. Это обеспечивается включением функции сброса при падении питающего напряжения VСС ниже порога защиты VLV (Low Voltage) -2-.6 В. Если уровень напряжения не снизится ниже уровня работоспособности КМОП-логики VCMOS (1.2 В), то возможно сохранение содержимого памяти МК и продолжение нормальной работы после восстановления VСС и автосброса. Это позволяет защитить МК от кратковременных "провалов" питающего напряжения.

Пока сброс активен, на выход /AS подаются импульсы внутренней синхронизации, выход /DS имеет низкий потенциал, R//W -высокий.

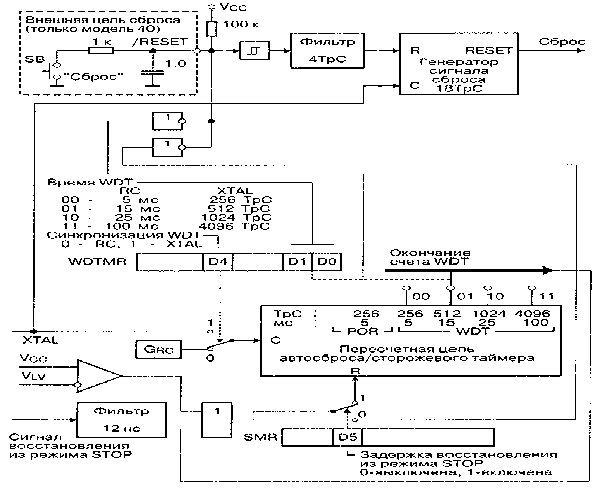

Обобщенная структурная схема сброса и сторожевого таймера показана на рис. 1.7.

Рис. 1.7. Схема сброса/сторожевого таймера

Схема содержит генератор сигнала внутреннего сброса, синхронизируемого импульсами основного генератора XTAL. Этот генератор обеспечивает минимальную длительность сигнала сброса 18 периодов TpC частоты XTAL. Запуск генератора осуществляется через фильтр длительности в 4 TpC. Иначе говоря, если длительность запускающего сигнала будет меньше 4 TpC, то сброса не произойдет. Если запускающий сигнал длиннее 18 TpC, то сброс будет удерживаться на время этого сигнала плюс 18 TpC.

Объединение сигналов запуска сброса осуществляется по схеме "монтажное ИЛИ", поэтому к внешнему выводу МК /RESET (только для модели 40) можно подключать схемы с выходными каскадами с открытым стоком. Для сброса МК с помощью кнопки SB "Сброс" следует применять внешнюю RC-цепь, показанную на том же рисунке. Для возможности использования RC-цепи вход запуска дополнен триггером Шмитта.

Таймер автосброса POR (Power-On Reset) и сторожевой таймер WDT (Watch-Dog Timer) выполнены в виде пересчетной цепи, которая, в общем случае, синхронизируется от дополнительного RC-генератора GRC или от основного генератора XTAL. Таймер POR имеет для всех моделей постоянное время, а таймер WDT -программируемое (за исключением моделей 02, 03, 04 и 08).

Запуск таймера автосброса POR осуществляется в следующих случаях:

- если уровень VСС поднимается выше уровня VLV;

- если становится активным сигнал восстановления из режима STOP;

- если имеет место окончание счета сторожевого таймера WDT.

В первом случае сигнал запуска вырабатывается специальным компаратором А. Во втором случае паразитные всплески сигнала источника подавляются фильтром 12 нс.

Во всех этих случаях происходит запуск таймера автосброса POR, время задержки которого гарантирует окончание переходных процессов в цепи питания VСС и выход на нормальный режим основного генератора синхронизации XTAL, после чего корректно выполняется внутренний сброс МК.

При восстановлении из режима STOP в случае применения LCили RC-времязадающих цепей основного генератора (см. п.1.2.3) нет необходимости выдерживать задержку автосброса, т.к. эти конфигурации генератора имеют малое время установления. Для сокращения задержки восстановления из режима STOP в этом случае сигнал от источника может быть подан непосредственно на вход запуска генератора сигнала сброса. При этом необходимо, чтобы сигнал от источника восстановления имел длительность не менее 4 TpC.

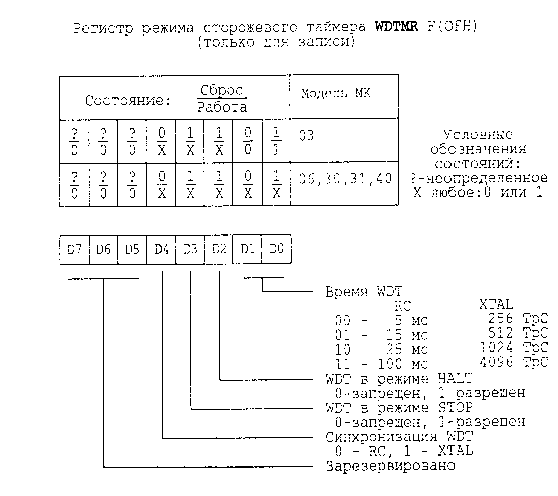

В МК, имеющих расширенную группу регистров F (модели 03, 06, 30, 31, 40), управление схемой сброса / сторожевого таймера осуществляется с помощью регистров режима сторожевого таймера WDTMR (Watch-Dog Timer Mode Register) и режима восстановления из режима STOP-SMR (STOP-Mode Recovery Register). Логика управления понятна из рисунка. Следует отметить, что поскольку генератор основной синхронизации выключается в режиме STOP, прежде чем перейти в этот режим необходимо, чтобы бит D4 WDTMR был установлен в состояние 0. Необходимо помнить, что регистр WDTMR доступен для записи только в течение первых 64 тактов (128 TpC) процессора после сброса, вызванного любым источником. Назначение разрядов регистра WDTMR полностью показано на рис. 1.8.

Рис. 1.8. Регистр WDTMR

Запуск и обновление сторожевого таймера осуществляется специальной командой WDT в рабочем режиме выполнения программы RUN. После однократного выполнения этой команды сторожевой таймер постоянно разрешен. Поэтому программа МК должна предусматривать периодическое повторение (с периодом, меньшим установленного времени сторожевого таймера) команды WDT. Это должно быть обеспечено программистом. В этом случае, при нормальной работе процессора сторожевой таймер будет периодически перезапускаться и не достигнет состояния окончания счета. При "зависании" процессора сторожевой таймер достигает состояния окончания счета, что вызывает запуск автосброса МК и выполнение программы с начала. Работа WDT в режимах HALT и STOP разрешается путем программирования соответствующих битов D2 и D3 регистра WDTMR. В этом случае, при переходе в соответствующий режим, WDT продолжает свою работу.

В модели 03 сторожевой таймер имеет фиксированную задержку 15 мс (при синхронизации от GRC) или 512TpC (при синхронизации от XTAL), а состояние битов D1 и D0 регистра WDTMR должно быть 01.

В моделях 02, 04, 08 регистры WDTMR и SMR отсутствуют, поэтому схема имеет фиксированную конфигурацию (соответствует изображенным на рис.1.7 положениям переключателей). Разрешение работы сторожевого таймера в режиме HALT осуществляется исполнением специальной команды WDH (выполняется до перехода в режим HALT). В режиме STOP в этих МК работа сторожевого таймера запрещена.

Запрещение работы сторожевого таймера во всех моделях МК происходит при выполнении внутреннего сброса. Исключение составляют некоторые модели (или отдельные модификации) имеющие программируемый (масочно или однократно) бит постоянного разрешения WDT (Permanent WDT). Если этот бит запрограммирован, то WDT постоянно разрешен и запрещение работы его после сброса не происходит.

Таким образом, функция сброса и сторожевой таймер обеспечивают корректный начальный запуск программы и перезапуск в случае сбоя программы.

1.2.5. Порты ввода/вывода

МК Z8 имеет до 32 линий ввода/вывода, сгруппированных в четыре восьмибитных порта Р0, Р1, Р2, Р3 (физическое наличие соответствующих выводов портов для каждой модели МК указано в табл.1.2). Порты размещены в адресном пространстве регистрового файла по адресам соответственно 00H, 01H, 02H, 03H.

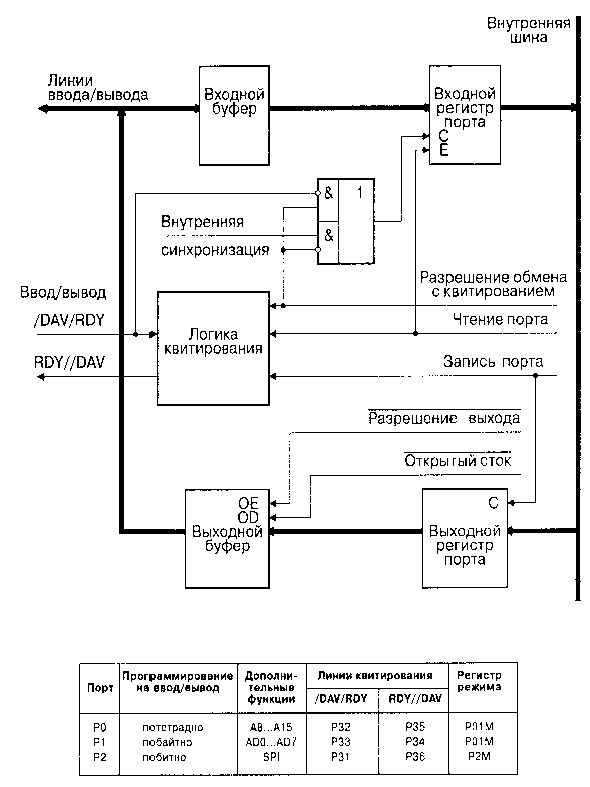

Порты Р0, Р1 и Р2 построены по типовой структуре, показанной на рис. 1.9. Каждый порт имеет входной и выходной регистры, входной и выходной буферы. Выходные буферы -двухтактные, однако, могут программироваться как схемы с открытым стоком (Open Drain). Кроме того, выходные буферы могут быть переведены в малошумящий режим.

Рис. 1.9. Структурная схема портов P0, P1 и P2

Работа линий портов может программироваться на ввод или вывод: Р0 -потетрадно, Р1 -побайтно (т.е. целиком), а Р2 -побитно (см. табл. на рис. 1.9). Порты могут работать в режиме синхронного программного обмена, в режиме обмена с квитированием, в режиме стробируемого ввода/вывода.

При синхронном программном обмене ввод или вывод реализуется в момент исполнения команд чтения или записи регистра порта. При этом внешнее устройство должно быть постоянно готово к обмену.

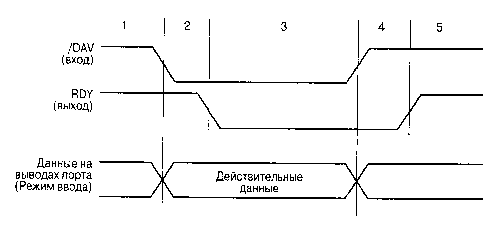

Режим обмена с квитированием или "рукопожатием" (Handshake) заключается в том, что МК и внешнее устройство обмениваются сигналами (квитанциями) ГОТОВНОСТИ к обмену -RDY (Ready) и ДЕЙСТВИТЕЛЬНОСТИ ДАННЫХ -/DAV (Data is Available). Ввод и вывод с квитированием подробно поясняются временными диаграммами, рис.1.10 и 1.11.

| Состояние 1. | Сигнал RDY имеет высокий уровень, что указывает MK принять данные. | |

| Состояние 2. | Внешнее устройство помещает данные на выводы порта и активизирует сигнал /DAV. Это приводит к фиксации данных во входном регистре порта МК и генерирования запроса прерывания. | |

| Состояние 3. | МК переводит выход RDY в низкое состояние, сигнализируя внешнему устройству, что данные зафиксированы. | |

| Состояние 4. | Внешнее устройство возвращает линию /DAV в высокое состояние после получения низкого уровня сигнала RDY. | |

| Состояние 5. | МК должен среагировать на запрос прерывания и прочитать содержимое порта для завершения последовательности квитирования. На линии RDY устанавливается высокий уровень тогда и только тогда, когда порт уже прочитан и /DAV имеет высокий уровень. Это возврощает интерфейс в его начальное значение. |