Курсовая работа: Пространственно-временной коммутатор 7x7

Курсовая работа: Пространственно-временной коммутатор 7x7

Курсовая работа: Пространственно-временной коммутатор 7x7

Федеральное агентство по образованию Российской Федерации

Уфимский государственный авиационный технический университет

Кафедра АСУ

КУРСОВАЯ РАБОТА

по коммутации

на тему: Пространственно-временной коммутатор 7x7

ОГЛАВЛЕНИЕ

коммутатор преобразователь дешифратор

1. Задание

2. Введение

3. Разработка функциональной схемы

4. Назначение основных элементов коммутатора и принцип их работы

4.1 Последовательно-параллельный и параллельно-последовательный преобразователи, стробирующие регистры

4.2 Дешифратор

4.3 Речевое и адресное запоминающие устройства

4.4 Счетчик

4.5 Мультиплексоры

5. Расчет блокировок коммутационного поля в режиме индивидуального искания

6. Заключение

1. Задание

Разработать пространственно-временной коммутатор потоков DS1 (30 каналов) и рассчитать блокировки построенного на его основе коммутационного поля в режиме индивидуального искания.

Исходные данные: общее число входов коммутационного поля N=4;

число входов одного коммутатора n=2;

число коммутаторов в среднем звене m=4;

интенсивность нагрузки Y =0,8 Эрл.

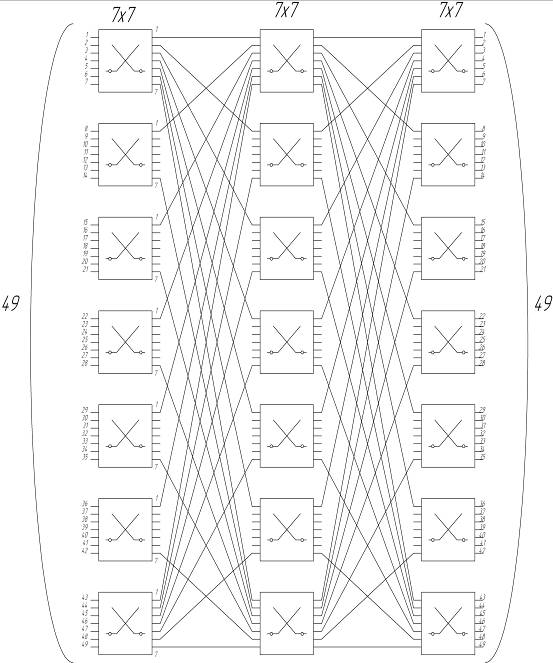

Структура коммутационного поля, соответствующая исходным данным, представлена на рис. 1.1.

Рис. 1.1. Структура коммутационного поля.

2. Введение

Вторая половина ХХ века ознаменовалась переходом от так называемого индустриального способа общественного производства к информационному, в котором главенствующую роль начинает играть информация как основной критерий развития. Как следствие, повышаются требования к качеству систем коммутации и способам передачи, для повышения качества сигнала. Изобретение компьютеров тем более усилило процесс эволюции, так как резко возросшие объемы предаваемой информации, вводили проблему с ее обработкой, и введение дополнительного аналогового оборудования уже не могло решить эту проблему. Необходимо было создавать качественно новые системы связи.

Данную проблему удалось решить к началу 1980-х годов, когда началось чувствоваться влияние сетей ISDN, концепции Интеллектуальной сети, идеи Информационной магистрали. Одной из наиболее существенных технологий среди перечисленных выше являются цифровые АТС с программным управлением. Эпоху цифровой реализации телекоммуникационной сети предопределило наличие двух очень важных устройств: кодеков и модемов. Именно они, наряду с цифровизацией многоканальной электросвязи – систем передачи с ИКМ, обусловили появление цифровых систем коммутации.

Переход на цифровую передачу и коммутацию немедленно привел к резкому возрастанию числа обсуживаемых абонентов и улучшению качества речи, к уменьшению массогабаритных параметров, а как следствие экономия сырья на изготовление микросхем; значительно возросла надежность оборудования, ввиду использования автоматизированного процесса изготовления и настройки. Также были введены вспомогательные и дополнительные виды обслуживания абонентов (например, услуги Интеллектуальной сети).

Особенности цифровых коммутационных устройств с импульсно-кодовой модуляцией (ИКМ) сигналов: процессы на входах, выходах и внутри устройств согласованы по частоте и времени (синхронные устройства).

3. Разработка функциональной схемы

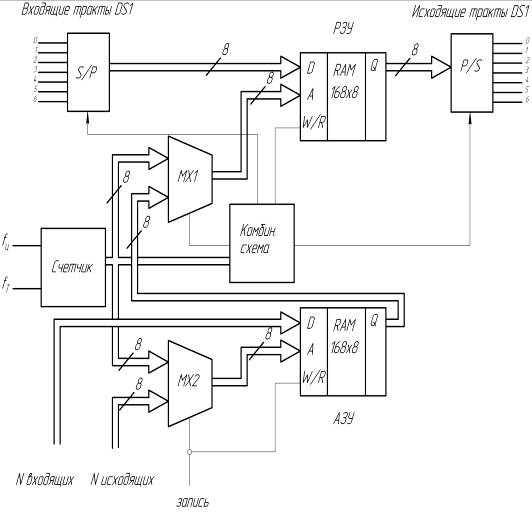

Структурная схема пространственно - временного коммутатора 7x7 представлена на рис. 3.1.

Рис. 3.1. Структурная схема пространственно - временного коммутатора 7x7:

S/P - последовательно-параллельный преобразователь;

P/S - параллельно-последовательный преобразователь;

РЗУ - речевое запоминающее устройство;

АЗУ - адресное запоминающее устройство;

СЧ - счетчик;

МX1 - мультиплексор адреса РЗУ;

МX2 - мультиплексор адреса АЗУ.

Данный коммутатор осуществляет пространственно-временную коммутацию входящих трактов ИКМ в исходящие.

Последовательно-параллельный преобразователь S/P осуществляет преобразование входящих ИКМ-трактов, представленных в последовательной форме, в параллельную.

РЗУ предназначено для записи и хранения в определенных ячейках, по адресам счетчика, кодовых комбинаций и считывания их в нужный момент времени.

АЗУ используется для записи и хранения информации о том, какой входящий и исходящий канал необходимо скоммутировать, и в последующем обеспечивает считывание в нужный момент времени номера входящего канала на адресные входы РЗУ при помощи счетчика.

Счетчик в свою очередь выдает адреса на РЗУ для записи по ним входящих каналов, а на АЗУ для считывания по ним номеров входящих каналов.

Дешифратор, получая адреса со счетчика, выдает логическую 1 на соответствующих выводах, что необходимо для разрешения параллельной загрузки информации на регистры S/P, и P/S при преобразовании кода в последовательную форму в исходящем тракте.

Мультиплексор MХ1 РЗУ осуществляет переключение сигналов со счетчика и сигналов, приходящих с АЗУ на выход, осуществляя тем самым запись и считывание по приходящим адресам.

Принцип работы мультиплексора МХ2 АЗУ аналогичен.

Параллельно-последовательный преобразователь P/S преобразует параллельную кодовую комбинацию с выхода РЗУ в последовательную форму для последующей коммутации с заданным исходящим каналом.

Пример коммутации 3-го входящего канала в 8-й исходящий представлен на временных диаграммах (Приложение В).

Установим основные требования к элементам функциональной схемы коммутатора:

Разрядность шины счетчика ![]() , где скобки

, где скобки ![]() означают

округленное до целого в большую сторону значение. Для коммутатора 7Ч7

входящих/исходящих трактов ИКМ-24 получим

означают

округленное до целого в большую сторону значение. Для коммутатора 7Ч7

входящих/исходящих трактов ИКМ-24 получим

![]()

Так как при считывании с РЗУ под

действием адресной информации, приходящей с выхода АЗУ (через мультиплексор

адреса), содержимое каждой ячейки речевой памяти может быть извлечено в какой-либо

канальный интервал исходящего тракта, то, очевидно, должны адресоваться все

ячейки РЗУ. Поскольку таких ячеек в РЗУ ![]() , то для их считывания необходима

адресная шина шириной не менее

, то для их считывания необходима

адресная шина шириной не менее ![]() разрядов.

разрядов.

С другой стороны, при емкости

коммутатора nЧm цифровых трактов, количество канальных интервалов на его выходе

равно mK (содержание речевой памяти может считаться в mK временных интервалах,

позиции которых определят моменты считывания адресных слов из АЗУ).

Следовательно, емкость АЗУ должна быть равна ![]() -разрядных ячеек. Для данного

коммутатора

-разрядных ячеек. Для данного

коммутатора ![]() .

.

Очевидно, что для исключения потери информации содержимого входящих цифровых трактов, за время цикла (Тц) необходимо успеть осуществить запись nK восьмиразрядных слов в РЗУ и считать их оттуда. Т.е. на запись и считывание одного канального слова в РЗУ квадратного коммутатора должно отводиться время не более

![]() ,

,

что определяет требование по быстродействию речевого ОЗУ при заданном числе входных каналов или, наоборот, требования к количеству входящих канальных интервалов или цифровых трактов при заданном быстродействии ОЗУ

![]() .

.

Все вышеперечисленные требования отражены на рис. 3.1.

4. Назначение основных элементов коммутатора и принцип их работы

4.1 Последовательно-параллельный и параллельно-последовательный преобразователи, стробирующие регистры

В последовательно-параллельном преобразователе используются 15 регистров К155ИР13. Первые восемь из них работают в режимах параллельной загрузки и сдвига вправо (режим определяется сигналами, приходящими с дешифратора), данные с входящих ИКМ трактов поступают на параллельные входы D0-D7 8 регистров, а снимаются с выходов Q7. Затем данные поступают на входы последовательного ввода данных остальных 7 регистров (второй ряд) и сдвигаются вправо, что необходимо для синхронного вывода данных с последовательно-параллельного преобразователя, причем каждый из 7 этих регистров осуществляет задержку на разное число тактов, так регистр обрабатывающий младший разряд кода сдвигает принятый импульс на 7 тактов, регистр обрабатывающий следующий разряд – соответственно на 6 тактов и т.д.

Элементная база и принцип действия параллельно-последовательного преобразователя аналогичны. Так как коммутатор 7х7, то в 8-ом канальном интервале полезных данных не содержится, и в параллельно-последовательном преобразователе достаточно использовать 13 регистров: 7 в режиме параллельной загрузки и сдвига, 6 только в режиме сдвига вправо.

Так основным критерием коммутационных устройств с ИКМ-модуляцией является согласование всех входов и выходов по частоте и времени (синхронные устройства), то для надлежащей работы схемы необходимо применять стробирующие регистры задержки на 1 такт.

Рис. 4.1. Микросхема К155ИР13.

Микросхема К155ИР13 – универсальный, восьмиразрядный, синхронный регистр сдвига (рис. 4.1). Каждая операция продолжается в регистре не более 20 нс. Синхронную работу регистру обеспечивают специальные входы выбора режима S0 и S1 (таблица 4.1). Таблица 4.2 содержит сочетания уровней на этих входах, позволяющие переводить регистр в тот или иной режим. Кроме однотипных параллельных входов D0-D7, имеются также дополнительные D-входы: DR – вход последовательного ввода данных при сдвиге информации вправо, DL – вход последовательного ввода данных при сдвиге информации влево.

При параллельной загрузке слово,

подготовленное на входах D0-D7, появится на выходах Q0-Q7 после прихода

последующего перепада тактового импульса на входе С. Низким уровнем на входе ![]() все выходные

сигналы устанавливаются на низкий уровень. Регистр потребляет ток 116 мА,

тактовая частота его может превышать 25 МГц.

все выходные

сигналы устанавливаются на низкий уровень. Регистр потребляет ток 116 мА,

тактовая частота его может превышать 25 МГц.

Таблица 4.1

Назначение выводов микросхемы К155ИР13

| Выводы | Назначение | Обозначение |

| 3,5,7,9,15,17,19,21 | Информационные входы | D0 - D7 |

| 11 | Вход синхронизации | C |

| 2 | Сдвиг вправо | DR |

| 22 | Сдвиг влево | DL |

| 1,23 | Выбор режима | S0 ,S1 |

| 13 | Вход сброса | R |

| 4,6,8,10,14,16,18,20 | Информационные выходы | Q0–Q7 |

| 24 | Питание | Ucc |

| 12 | Общий | 0 |

Таблица 4.2

Состояния регистра К155ИР13

| Режим работы | Вход | Выход | ||||||||

| С |

|

S1 | S0 | DR | DL | Dn | Q0 | Q1–Q6 | Q7 | |

| Сброс | х | Н | х | х | х | х | х | Н | Н – Н | Н |

| Хранение | | В | н | н | х | х | х | q0 | q1– q6 | q7 |

| Сдвиг влево | | В | в | н | х | н | х | q1 | q2 –q7 | Н |

| | В | в | н | х | в | х | q1 | q2 –q7 | В | |

| Сдвиг вправо | | В | н | в | н | х | х | Н | q0 –q5 | q6 |

| | В | н | в | в | х | х | В | q0 –q5 | q6 | |

| Параллельная загрузка | | В | в | в | в | х | dn | d0 | d1-d6 | d7 |

4.2 Дешифратор

Дешифратор К155ИД10 (рис. 4.2)

преобразует трехразрядный двоичный код, поступающий на входы DI1,

DI2 и DI4. Дешифратор К155ИД10

формирует сигналы параллельной загрузки, которые поступают на вход S0 первого ряда регистров К155ИР13. На входы DI1 подается сигнал частотой ![]() , на DI2 –

, на DI2 –![]() , на DI4 –

, на DI4 – ![]() со счетчика; на вход E подается уровень логического нуля. Таблица истинности

микросхемы К155ИД10 приведена в таблице Время задержки распространения сигнала

от адресного входа до выхода 50 нс. Ток потребления микросхемы 70 мА. Таблица 4.3

отражает все возможные состояния дешифратора.

со счетчика; на вход E подается уровень логического нуля. Таблица истинности

микросхемы К155ИД10 приведена в таблице Время задержки распространения сигнала

от адресного входа до выхода 50 нс. Ток потребления микросхемы 70 мА. Таблица 4.3

отражает все возможные состояния дешифратора.