Реферат: Разработка микропроцессорного устройства цифрового фильтра

Реферат: Разработка микропроцессорного устройства цифрового фильтра

W®ADCON0

0x0C®W

Разрешить

прерывание

W®FSR АЦП

Разрешить

глобальное

Сброс INDF прерывание

FSR + 1 Пуск АЦП

![]()

![]()

1 2

2

3

2

3

Вычисление

А11UM1с сох- Вычисление

ранением зна- A32YN2YK2=

чения =A32(YN2+YK2)

с сохранением

значения

значения

Вычисление

B11YN1 с сох-

ранением зна- Вычисление

чения B31YL1

Вычисление

В12YN2

ВычислениеYLL

= A31YN1YK1+

Вычисление + A32YN2YK2-

YNN=А11UM1- - B31YL1 с сох-

- B11YN1- ранением зна-

- В12YN2 с сох- чения

ранением зна-

чения

чения

Вычисление YK1 ® W

A21UM1 с сох-

ранением зна-

чения

чения

Вычисление W ® YK2

B21YK1

Вычисление YK ® W

YK=А21UM1-

- B21YK1 с сох-

ранением зна-

чения

W ® YK1

W ® YK1

Вычисление

A31YN1YK1 =

=A31(YN1+YK1) Вычисление

с сохранением A10UM

значения

3

4

4 6 5

![]()

Вычисление

YN =A10UM+ UM ® W

+YNN

с сохранением

с сохранением

значения

W ® UM1

Вычисление

YL=A30(YN+

YL=A30(YN+

![]() +YK)+YLL

+YK)+YLL

с сохранением

значения

ОСТАНОВ

ОСТАНОВ

Передача знач-

чения YL на

порт B

YN1 ® W

W ® YN2

YN ® W

W ® YN1

YL ® W

![]()

5

Рисунок 4.2 - Алгоритм программы проектируемого устройства

5 РАЗРАБОТКА ПРОГРАММЫ НА ЯЗЫКЕ АССЕМБЛЕР

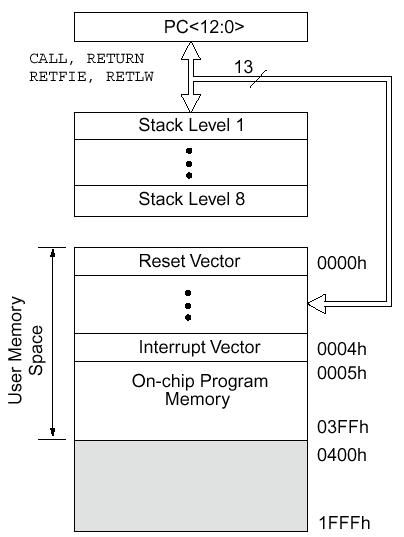

Прежде чем приступить к написанию программы необходимо учесть спецификацию ПЗУ микроконтроллера. Организация ПЗУ изображена на рисунке 5.1

Рисунок 5.1 – Организация ПЗУ PIC16C71

Из рисунка видно, что начало программы пользователя может быть расположено ниже адреса 0004h. Адрес 0000h – вектор сброса, 0004h – вектор прерывания. По этим адресам перед началом программирования, как правило, прописывают безусловный переход на программу пользователя и безусловный переход на программу обработки прерывания соответственно. Так как в случае нашей системы устройство, осуществляющее запрос прерывания, одно, то по адресу 0004h можно прописывать начало программы обработки прерывания.

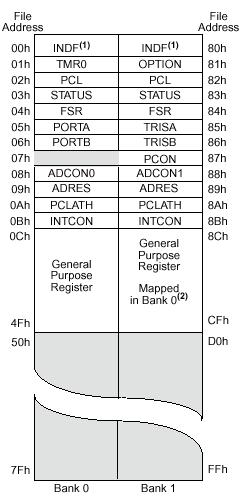

Также при программировании обязательно нужно учесть спецификацию банков ОЗУ. Структура ОЗУ изображена на

рисунке 5. При обращении к регистрам ОЗУ каждый раз необходимо программно переключаться между банками ОЗУ, в зависимости от того в каком банке находится регистр. Ассемблер, поставляемый производителем, позволяет вначале всем регистрам присвоить вместо адреса определенное имя. Это удобно для составления программы.

Рисунок 5.2 – Организация ОЗУ PIC16C711

Сначала напишем программу обработки прерывания. Занесем программу в таблицу - 1 с адресами ПЗУ и комментариями.

Таблица 5.1

| Адрес | Метка | Мнемонический код | Комментарии | Циклы |

| ORG 0x004 | Директива | |||

| 0004h | MOVWF W_TEMP | Сохранение содержимого W в W_TEMP | 1 | |

| 0005h | MOVF STATUS, 0 | Пересылка содержимого STATUS в W | 1 | |

| 0006h | MOVWF STATUS_TEMP | Сохранение W в STATUS _TEMP | 1 | |

| Продолжение таблицы 5.1 | ||||

| 0007h | BCF STATUS, RP0 | Выбор банка 0 | 1 | |

| 0008h | MOVF ADRES, 0 | Пересылка результата АЦП в W | 1 | |

| 0009h | MOVWF UM | Пересылка W в UM | ||

| 000Ah | MOVF STATUS_TEMP, 0 | Пересылка STATUS_TEMP в W | 1 | |

| 000Bh | MOVWF STATUS | Пересылка W в STATUS | 1 | |

| 000Ch | MOVF W_TEMP, 0 | Пересылка W_TEMP в W | 1 | |

| 000Dh | RETFIE | Возврат прерывания | 2 | |

Программу, реализующую математическую модель фильтра начнем с адреса 000Eh и разместим в таблицу 5, 2.

Таблица 5.2

| Адрес | Метка | Мнемонический код | Комментарии | Циклы |

| ORG 0x00E | Директива | |||

| 000Eh | MOVLW 0xFF | Пересылка 0xFF в аккумулятор | 1 | |

| 000Fh | BSF STATUS, RP0 | Выбор банка 1 | 1 | |

| 0010h | MOVWF TRISA | Порт А – Вход | 1 | |

| 0011h | CLRF TRISB | Порт В – Выход | 1 | |

| 0012h | MOVLW 0x18 | Организация счетчика СOUNT | 1 | |

| 0013h | BCF STATUS, RP0 | Выбор банка 0 | 1 | |

| 0014h | MOVWF COUNT | Организация счетчика | 1 | |

| 0015h | MOVLW 0x0C | Адрес начальной ячейки в ОЗУ | 1 | |

| 0016h | MOVWF FSR | Пересылка адреса начальной ячейки в FSR | 1 | |

| 0017h | M1: | CLRF INDF | Обнуление текущей ячейки памяти | 1 |

| 0018h | INCF FSR, 1 | Адрес + 1 | 1 | |

| 0019h | DECF COUNT | Счетчик – 1 | 1 | |

| 001Ah | BTFSS STATUS, Z | Условный переход по 1 значению флага нулевого результата | 1(2) | |

| 001Bh | GOTO M1 | 2 | ||

| 001Ch | M2: | BSF STATUS,RP0 | Выбор банка 1 | 1 |

| 001Dh | CLRF ADCON1 | RA0-RA3 Входы АЦП | 1 | |

| 001Eh | MOVLW 0xC1 | 1 | ||

| 001Fh | BCF STATUS,RP0 | Выбор банка 0 | 1 | |

| 0020h | MOVWF ADCON0 | АЦП включен, работает канал0 (RA0), частота 32Tosc. | 1 | |

| 0021h | BSF INTCON ADIE | Разрешить прерывание АЦП | 1 | |

| 0022h | BSF INTCON GIE | Разрешить глобальное прерывание | 1 | |

| 0023h | BSF ADCON0, GO | Запустить АЦП | 1 | |

| 0024h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0025h | RRF UM1, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0026h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0027h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0028h | MOVWF A11UM1 | W® A11UM1 | 1 | |

| 0029h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 002Ah | RRF YN1, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 002Bh | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 002Ch | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 002Dh | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 002Eh | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| Продолжение таблицы 5.2 | ||||

| 002Fh | BCF STATUS, C | 1 | ||

| 0030h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0031h | MOVWF B11YN1 | W® B11YN1 | 1 | |

| 0032h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0033h | RRF YN1, 0 | Циклический сдвиг вправо через триггер переноса | ||

| 0034h | ADDWF W, 0 | W=W+W | 1 | |

| 0035h | ADDWF W, 0 | W=W+W | 1 | |

| 0036h | ADDWF B11YN1 | W=W+ B11YN1 | 1 | |

| 0037h | SUBWF A11UM1, 0 | W= A11UM1- W | 1 | |

| 0038h | MOVWF YNN | W® YNN | 1 | |

| 0039h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 003Ah | RRF UM1, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 003Bh | MOVWF A21UM1 | W® A21UM1 | 1 | |

| 003Ch | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 003Dh | RRF YK1, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 003Eh | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 003Fh | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0040h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0041h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0042h | SUBWF A21UM1, 0 | W= A21UM1- W | 1 | |

| 0043h | MOVWF YK | W® YK | 1 | |

| 0044h | MOVF YN1, 0 | YN1®W | 1 | |

| 0045h | ADDWF YK1 | W=W+ YK1 | 1 | |

| 0046h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0047h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0048h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0049h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 004Ah | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 004Bh | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 004Ch | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 004Dh | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 004Eh | MOVWF A31YN1YK1 | W® A31YN1YK1 | 1 | |

| 004Fh | MOVF YN2, 0 | YN2®W | 1 | |

| 0050h | ADDWF YK2 | W=W+ YK2 | 1 | |

| 0051h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0052h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0053h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0054h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0055h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0056h | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0057h | MOVWF A32YN2YK2 | W® A32YN2YK2 | 1 | |

| 0058h | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0059h | RRF YL1, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| Продолжение таблицы 5.2 | ||||

| 005Ah | ADDWF W, 0 | W=W+W | 1 | |

| 005Bh | ADDWF W, 0 | W=W+W | 1 | |

| 005Ch | SUBWF A32YN2YK2, 0 | W= A32YN2YK2- W | 1 | |

| 005Dh | ADDWF A31YN1YK1 | W=W+ A31YN1YK1 | 1 | |

| 005Eh | MOVWF YLL | W® YLL | 1 | |

| 005Fh | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 0060h | NOP | Ничего не выполнять | 1 | |

| 0061h | NOP | 1 | ||

| 0062h | NOP | 1 | ||

| 0063h | NOP | 1 | ||

| 0064h | NOP | 1 | ||

| 0065h | NOP | 1 | ||

| 0066h | NOP | 1 | ||

| 0067h | NOP | 1 | ||

| 0068h | NOP | 1 | ||

| 0069h | NOP | 1 | ||

| 006Ah | NOP | 1 | ||

| 006Bh | NOP | 1 | ||

| 006Ch | NOP | 1 | ||

| 006Dh | NOP | 1 | ||

| 006Eh | NOP | 1 | ||

| 006Fh | NOP | 1 | ||

| 0070h | NOP | 1 | ||

| 0071h | NOP | 1 | ||

| 0072h | NOP | 1 | ||

| 0073h | NOP | 1 | ||

| 0074h | MOVF YK1, 0 | YK1®W | 1 | |

| 0075h | MOVWF YK2 | W® YK2 | 1 | |

| 0076h | MOVF YK, 0 | YK ®W | 1 | |

| 0077h | MOVWF YK1 | W® YK1 | 1 | |

| 0078h | RRF UM, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 0079h | ADDWF YNN | W=W+ YNN | 1 | |

| 007Ah | MOVWF YN | W® YN | 1 | |

| 007Bh | ADDWF YK | W=W+ YK | 1 | |

| 007Ch | BCF STATUS, C | Очистка триггера переноса | 1 | |

| 007Dh | RRF W, 0 | Циклический сдвиг вправо через триггер переноса | 1 | |

| 007Eh | ADDWF W, 0 | W=W+W | 1 | |

| 007Fh | ADDWF YLL | W=W+ YLL | 1 | |

| 0080h | MOVWF YL | W® YL | 1 | |

| 0081h | MOVWF PORTB | W® PORTB | 1 | |

| 0082h | MOVF YN1, 0 | YN1®W | 1 | |

| 0083h | MOVWF YN2 | W® YN2 | 1 | |

| 0084h | MOVF YN, 0 | YN ®W | 1 | |

| 0085h | MOVWF YN1 | W® YN1 | 1 | |

| 0086h | MOVF YL, 0 | YL ®W | 1 | |

| 0087h | MOVWF YL1 | W® YL1 | 1 | |

| 0088h | MOVF UM, 0 | UM ®W | 1 | |

| 0089h | MOVWF UM1 | W® UM1 | 1 | |

| 008Ah | GOTO M2 | Безусловный переход на метку | 1 | |

| END | ||||

| Всего вместе с программой обработки прерывания | 283 | |||

Время выполнения программы 56 мкс.

Операции NOP предназначены для синхронизации работы АЦП с программой. Также для этой цели было добавлено 4 команды перед операциями над текущим значением отсчета. В составленном алгоритме данные коррекции небыли предусмотрены. Время выполнения программы, реализующей цифровой фильтр, равно 49 мкс. Интервал дискретизации сигнала равен 24,6 мкс, соответственно частота дискретизации равна 41000Гц. В программе используются два перехода: один для обнуления ОЗУ, другой – для возврата программы на место запуска АЦП. При использовании более современных PIC процессоров возможно исключение операций NOP.

6 РАЗРАБОТКА И ОПИСАНИЕ ПРИНЦИПИАЛЬНОЙ СХЕМЫ

Для технической реализации ЦФ необходимы следующие элементы:

- процессор;

- ЦАП;

- Блок питания от сети 220 В, 50 Гц.

Описание процессора:

Основным блоком ЦФ является процессор PIC16C711 (рис.6.1). Приведём краткую характеристику интересующих для данной задачи выводов процессора.

RA4/RTCC - Вход через триггер Шмита. Ножка порта ввода/вывода с открытым стоком или вход частоты для таймера/счетчика RTCC. RA0/AIN0 - Двунаправленная линия ввода/вывода. Аналоговый вход канала 0. Как цифровой вход имеет уровни ТТЛ.

RA1/AIN1 - Двунаправленная линия ввода/вывода. Аналоговый вход канала 1. Как цифровой вход имеет уровни ТТЛ.

RA2/AIN2 - Двунаправленная линия ввода/вывода.Аналоговый вход канала 2. Как цифровой вход имеет уровни ТТЛ.

RA3/AIN3/Vref - Двунаправленная линия ввода/вывода. Аналоговый вход канала 3. Как цифровой вход имеет уровни ТТЛ.

RB0/INT - Двунаправленная линия порта вывода или внешний вход прерывания. Уровни ТТЛ.

RB1 - RB5 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

RB6 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

RB7 - Двунаправленные линии ввода/ вывода. Уровни ТТЛ.

/MCLR/Vpp - Низкий уровень на этом входе генерирует сигнал сброса для контроллера. Активный низкий. Вход через триггер Шмитта.

OSC1 - Для подключения кварца, RC или вход внешней тактовой частоты.

OSC2 /CLKOUT - Генератор, выход тактовой частоты в режиме RC генератора, в остальных случаях - для подключения кварца.

Vdd - Напряжение питания.

Vss – Общий (земля).

RA2/AIN2 1 18 RA1/AIN1

RA3/AIN3/Vref RA0/AIN0

RA4/RTCC OSC1/CLKIN

/MCLR/Vpp OSC2/CLKOUT

Vss PIC16C711 Vdd

RB0/INT RB7

RB1 RB6

RB2 RB5

RB3 9 10 RB4

Рисунок 6.1 – Выводы процессора PIC16C711

Описание ЦАП:

В качестве ЦАП используется микросхема фирмы Analog Devices AD7302. Данный ЦАП имеет следующие основные характеристики:

AD7302 двойной, 8-битный ЦАП, который работает от однополярного источника питания с напряжением +2.7 - +5.5 В. AD7302 имеет интерфейс, совместимый параллельным выходом микропроцессоров и цифровых сигнальных процессоров (DSP). Интерфейс обладает высокоскоростными регистрами и двойной буферизированной логикой. Данные загружаются при повышенном уровне на CS или WR. С помощью пина ~A/B выбирают какой из 2 встроенных ЦАП будет использоваться.

Приведём краткую характеристику интересующих для данной задачи выводов ЦАП.

D7-D0 - Параллельные информационные входы. 8-битные данные загружаються во входной регистр AD7302 под управлением CS и WR.

CS - Выбор кристалла. Активный низкоуровневый логический ввод.

WR - Ввод записи. Активный низкоуровневый логический ввод. Используеться вместе CS и A/B, чтобы писать данные в регистр выбранного ЦАП.

A/B – Выбор ЦАП.

PD – Активный низкоуровневый ввод, используемый для перехода в режим потребления малой мощности.

LDAC – Логический ввод загрузки ЦАП. Когда на этот ввод подаеться низкий уровень, оба ЦАП синхронно обновляются со своими регистрами.

CLR – Асинхронный вход сброса. Когда на него подаеться низкий уровень, все регистры ЦАП обнуляються и на выход напряжение не поступает.

Vdd – Напряжение питания.

REFIN – Внешний ввод ссылки. Может использоваться как ссылка для обоих ЦАП. Диапазон этого ввода 1 В – Vdd/2.

AGND – Земля для аналоговой части микросхемы.

VoutB – Аналоговый вывод ЦАП B.

VoutA – Аналоговый вывод ЦАП А.

DGND – Земля для цифровой части схемы.

DB7 1 20 DGND

DB6 VoutA

DB5 VoutB

DB4 AGND

DB3 AD7302 REFIN

DB2 Vdd

DB1 CLR

DB0 LDAK

CS PD

WR 10 11 A/B

Рисунок 6.2 – Выводы ЦАП AD7302

Блок питания от сети 220 В, 50 Гц :

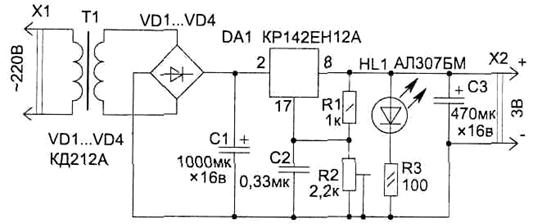

На рисунке 6.3 приведена простая схема блока питания на 3 В (ток в нагрузкеке 200 мА) с автоматической электронной защитой от перегрузки (Iз = 250 мА). Уровень пульсации выходного напряжения не превышает 1 мВ.В схеме в качестве источника опорного напряжения используется светодиод HL1. Трансформатор Т1 можно приобрести из унифицированной серии ТН любой, но лучше использовать самые малогабаритные ТИ1-127/220-50 или ТН2-127/220-50. Подойдут также и многие другие типы трансформаторов со вторичной обмоткой на 5...6 В. Конденсаторы С1...СЗ типа К50-35. Схема использует интегральный стабилизатор DA1, для нормальной работы микросхемы необходимо, чтобы входное напряжение превышало выходное не менее чем на 3,5 В. Это снижает КПД стабилизатора за счет тепловыделения на микросхеме — при низком выходном напряжении мощность, теряемая в блоке питания, будет превышать отдаваемую в нагрузку. Необходимое выходное напряжение устанавливается подстроечным резистором R2. Микросхема устанавливается на радиатор.

Рисунок 6.2 – Схема генератора

ВЫВОД

Спроектированная система является достаточно простой. Схема электрическая принципиальная составлялась на ПК с использованием пакета ACCEL. С помощью утилит, входящих в данный пакет, можно провести трассировку печатной платы по готовой схеме электрической принципиальной и довести проект до готового изделия.

По результатам курсового проекта можно оценить погрешности связанные с оцифровкой сигнала. Основную погрешность будет вносить ограниченная восемью разрядами шина АЦП, чем больше уровней квантования - тем лучше. Также, ввиду отсутствия операций с плавающей точкой, деление на два нечетных чисел будет давать неточный результат.

Для оцифровки аналоговых сигналов должно

выполняться условие ![]() . На практике

. На практике![]() и выше для улучшения

качества передаваемого сигнала. Спектр речевого сигнала качественной телефонии

составляет 0,3 – 3,4 кГц в соответствии с установленным международным

стандартом. Цифровой фильтр, спроектированный в ходе курсовой работы,

удовлетворяет требованиям обработки не только сигналов качественной речи, но и

сигналов с верхней частотой спектра 15..20кГц (музыка, каналы ШК и т.д.).

и выше для улучшения

качества передаваемого сигнала. Спектр речевого сигнала качественной телефонии

составляет 0,3 – 3,4 кГц в соответствии с установленным международным

стандартом. Цифровой фильтр, спроектированный в ходе курсовой работы,

удовлетворяет требованиям обработки не только сигналов качественной речи, но и

сигналов с верхней частотой спектра 15..20кГц (музыка, каналы ШК и т.д.).

СПИСОК ЛИТЕРАТУРЫ

1. Калабеков Б. А. Микропроцессоры и их применение в системах

передачи и обработки сигналов: Учеб. Пособие для вузов. – М.:

Радио и связь, 1988. – 368с.: ил.

2. Корнеев В. В., Киселев А. В. Современные микропроцессоры. – М.:НОЛИДЖ, 1998. – 240 с.; ил.

3. MICROCHIP PIC16/17 MICROCONTROLLER DATA BOOK.

4. Документация на CD, поставляемая компанией MICROCHIP.