Реферат: Перспективные интерфейсы оперативной памяти

Реферат: Перспективные интерфейсы оперативной памяти

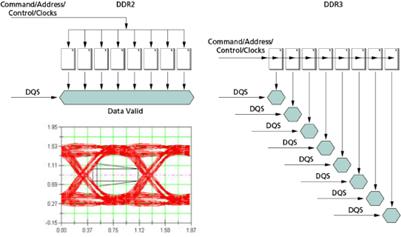

Различие между способом подачи адресов и команд, сигналов управления и тактовой частоты в модулях памяти DDR2 и DDR3 (на примере модулей, физический банк которых составлен из 8 микросхем разрядностью x8) представлено на рис. 7.

В модулях памяти DDR2 подача адресов и команд осуществляется параллельно на все микросхемы модуля, в связи с чем, например, при считывании данных, все восемь 8-битных элементов данных окажутся доступными в один и тот же момент времени (после подачи соответствующих команд и истечения соответствующих задержек) и контроллер памяти сможет одновременно прочитать все 64 бита данных.

В то же время, в модулях памяти DDR3 вследствие применения «пролетной» архитектуры подачи адресов и команд каждая из микросхем модуля получает команды и адреса с определенным отставанием относительно предыдущей микросхемы, поэтому элементы данных, соответствующие определенной микросхеме, также окажутся доступными с некоторым отставанием относительно элементов данных, соответствующих предыдущей микросхеме в ряду, составляющем физический банк модуля памяти. В связи с этим, с целью минимизации задержек, в модулях памяти DDR3, по сравнению с модулями DDR2, реализован несколько иной подход ко взаимодействию контроллера памяти с шиной данных модуля памяти. Он называется «регулировкой уровня чтения/записи» (read/write leveling) и позволяет контроллеру памяти использовать определенное смещение по времени при приеме/передачи данных, соответствующее «запаздыванию» поступления адресов и команд (а, следовательно, и данных) в определенную микросхему модуля. Этим достигается одновременность считывания (записи) данных из микросхем (в микросхемы) модуля памяти.

Рисунок 1.3 - Регулировка уровня чтения/записи (read/write leveling) в модулях памяти DDR3

Предположительно, модули памяти DDR3 будут предлагаться в вариантах от DDR3-800 до DDR3-1600 включительно, далее не исключено появление и более высокоскоростных модулей категории DDR3-1866. Рейтинг производительности модулей памяти DDR3 имеет значение вида «PC3-X», где X означает пропускную способность модуля в одноканальном режиме, выраженную в МБ/с (если быть точным — млн. байт/с). Поскольку модули памяти DDR3 имеют ту же разрядность, что и модули памяти DDR2 — 64 бита, численные значения рейтингов равночастотных модулей памяти DDR2 и DDR3 совпадают (например, PC2-6400 для DDR2-800 и PC3-6400 для DDR3-800).

Типичные схемы таймингов, предполагаемые в настоящее время для модулей памяти DDR3, выглядят весьма «внушительно» (например, 9-9-9 для DDR3-1600), однако не стоит забывать, что столь большие относительные значения таймингов, будучи переведенными в абсолютные значения (в наносекундах), учитывая все меньшее время цикла (обратно пропорциональное частоте шины памяти), становятся вполне приемлемыми. Так, например, задержка сигнала CAS# (tCL) для модулей памяти DDR3-800 со схемой таймингов 6-6-6 составляет 15 нс, что, конечно, несколько великовато по сравнению с «типичными» DDR2-800 со схемой таймингов 5-5-5, для которых tCL составляет 12.5 нс. В то же время, память типа DDR3-1600 со схемой таймингов 9-9-9 уже характеризуются величиной задержки tCL всего 11.25 нс, что находится на уровне DDR2-533 с достаточно низкими задержками (схемой таймингов 3-3-3). Таким образом, даже при предполагаемом на данный момент «раскладе» схем таймингов модулей памяти DDR3 можно ожидать постепенное снижение реально наблюдаемых задержек при доступе в память, вплоть до значений, типичных для нынешнего поколения модулей памяти DDR2. К тому же, не стоит забывать и о дальнейшем снижении задержек (и снижении таймингов) по мере развития технологии.

1.4 RAMBUS (RDRAM)

На данный момент существует только один способ повышения пропускной способности (BW — BandWidth) любой подсистемы — это увеличение либо частоты коммутации шины, либо ее "ширины" (разрядности). Совместное увеличение этих параметров довольно проблематично и имеет быстрое "насыщение", поскольку влияние электромагнитной интерференции (ЭМИ) и частотных эмиссий в этом случае возрастает нелинейно — EMI=kIAf2. Это обстоятельство вынуждает разработчиков идти на компромиссы. В противовес технологии SDRAM, где используется 64bit магистраль и частоты до 133MHz, Rambus DRAM предоставляет 16bit шину и результирующую частоту обмена до 800MHz, используя технологию DDR, передавая/принимая данные по фронту/срезу синхросигнала. Узкая шина и сверхвысокая частота значительно повышают эффективность использования и загрузку канала, максимально освобождая протокол от временных задержек. Итак, детально рассмотрим технологию Rambus DRAM.

Вообще, существует три разновидности памяти RDRAM, представляющие собой некую эволюцию развития технологии: Base (BRDRAM), Concurrent (CRDRAM) и Direct (DRDRAM). Отличие первого и второго совсем небольшие, а вот изменения последнего просто революционны. Причем, технологии Base и Concurrent настолько сильно переплетаются, что, в принципе, это одно и тоже.

Таблица 1.1

Характеристики различных видов памяти RDRAM

|

Основные типы технологии RDRAM |

|||

|

Параметр |

Base RDRAM |

Concurrent RDRAM |

Direct RDRAM |

| Частота синхронизации | 250-300 MГц | 300-350 MГц | 400 MГц |

| Результирующая частота (с учетом DDR) | 500-600 MГц | 600-700 MГц | 800 MГц |

| Пиковая пропускная способность | 500-600 Mбайт/с | 600-700 Mбайт/с | 1.6 Гбайт/с |

| Шина данных (базовая/ECC) | 8/9 бит | 8/9 бит | 16/18 бит |

| Загрузка 32bit протокола | 60% | 80% | 97-100 % |

| Интерфейс общего питания (CMOS) | 3.3 В | 3.3 В | 2.5 В |

| Размах активных уровней сигналов | 1.0 В | 1.0 В | 0.8 В |

| Диапазон напряжений "точка-точка" (RSL) | 1.5-2.5 В | 1.5-2.5 В | 1.0-1.8 В |

| Опорное напряжение | 2.0 В | 2.0 В | 1.4 В |

| Число высокоскоростных сигналов RSL | 13 | 13 | 30 |

| Число выводов для каждого из каналов | 32 | 32 | 72 |

| Тип корпуса микросхемы RDRAM | SHP/SVP | SHP/SVP | CSP (EBD/CBD) |

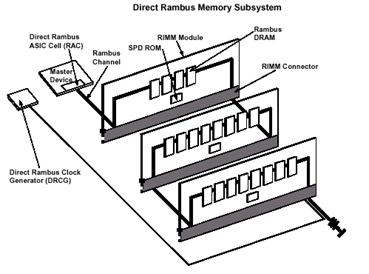

Технология Direct Rambus DRAM, разработанная компанией Rambus, представляет собой высокоскоростную замкнутую систему функционирования, которая имеет свою адаптированную логику управления и точно рассчитанные параметры. DRDRAM позволяет достичь очень больших пиковых скоростей передачи данных: до 1.6 Гбайт/с на один канал и до 6.4 Гбайт/с при четырех каналах. Вся подсистема состоит из следующих компонентов: основной контроллер (RMC — Rambus Memory Controller), канал (RC — Rambus Channel), разъем для модулей (RRC - Rambus RIMM Connector), модуль памяти (RIMM — Rambus In-line Memory Module), генератор дифференциальных синхроимпульсов (DRCG — Direct Rambus Clock Generator) и сами микросхемы памяти (RDRAM — Rambus DRAM). Физические, электрические и логические принципы и согласования, применяемые в системе, определены компанией Rambus и должны строго выполняться всеми производителями для соблюдения абсолютной совместимости ее частей, так она функционирует на очень большой частоте 600/711/800 МГц, синхронизируясь сигналом 300/350/400 MГц соответственно.

Рисунок 1.4 – Схематическое изображение подсистемы памяти Direct Rambus

Сигнальный протокол Direct Rambus основан на новом электрическом интерфейсе RSL (Rambus Signaling Levels), дающем возможность при помощи технологии удвоенной передачи данных (DDR — Double Data Rate) получить результирующую частоту 600/711/800 MГц и использовать стандартный CMOS-интерфейс (см. схему 1 и схему 2) сигналов управленияядра ASIC (Application Specific Integrated Circuit). Высокоскоростной протокол сигналов RSL использует низковольтный размах (Swing) номинальных напряжений логического "0" (VOH=1.8 В) и логической "1" (VOL=1.0 В) с разностью 0.8 В (VCOS=VOH-VOL).

За счет внешнего опорного напряжения (VREF=1.4 В) стандартного CMOS-интерфейса, генерирующегося при помощи резистивного делителя, логические значения "0" и "1" представляются как 2.5 В (VOH,CMOS) и 1.7 В (VOL,CMOS) соответственно, т.е. разрядность составляет все те же 800 мВ, чтобы сохранить совместимость дискретизации уровней.

Меры частотного "разнесения" сигнальных групп вынужденные, и направлены на разделение стандартных сигналов питания/контроля (CMOS), и высокоскоростных (RSL) командных сигналов и интерфейса приема/передачи данных для уменьшения паразитного воздействия ЭМИ и ВЧ-шумов коммутаций шины.

Тактовый генератор вырабатывает импульсы с частотой 267-400 MГц, которые распространяются от крайней точки канала к контроллеру (CTM — Clock To Master), где разворачиваются и по другой линии идут в обратном направлении (CFM — Clock From Master), после чего попадают на терминатор (нагрузку, VTERM=1.8 В). Четкое согласование становиться возможным благодаря двум блокам автоподстройки длительности задержки в библиотечном макроядре (RAC — Rambus ASIC Cell), которые производят синхронизацию исходящих и входящих сигналов: блок передачи (TDLL — Transmit Delay Locked Loop) и блок приема (RDLL — Receive Delay Locked Loop). Передача команд и данных (блок TDLL) основана на эффекте точной 180° квадратурной фазы, выполняемой в цикле CFM. Все сигналы, распространяющиеся по направлению к контроллеру, синхронизируются входящими тактовыми импульсами, а сигналы, исходящие из контроллера — импульсами, идущими по направлению к нагрузке (функции блока RDLL). В процессе работы каждый блок DLL периодически осуществляет частотную ре-калибровку, учитывая условия функционирования, температуру (документ JESD63), возможные девиации напряжения и частоты. Ре-синхронизация (Re-Sync) всех узлов подсистемы, включая физические интерфейсы типа сдвига уровня напряжения и восстановления синхросигналов, представляется отдельным особенным комплексом мер, поскольку с увеличением частоты, длина волны сигнала становиться более короткой относительно собственной сигнальной трассы. В этом случае полагаться на пассивные элементы задержки (например, RC-цепь), помогающие восстановить "плывущий" протокол синхронизации, довольно опасно, учитывая влияние температуры, напряжения и 3s-вариаций (зависимость сечения рассеяния электромагнитной волны от ее частоты).